# **CENICS 2014**

The Seventh International Conference on Advances in Circuits, Electronics and Micro-electronics

ISBN: 978-1-61208-379-7

November 16 - 20, 2014

Lisbon, Portugal

# **CENICS 2014 Editors**

Vladimir Privman, Clarkson University - Potsdam, USA

Pascal Lorenz, University of Haute Alsace, France

# **CENICS 2014**

# Foreword

The Seventh International Conference on Advances in Circuits, Electronics and Microelectronics (CENICS 2014), held between November 16-20, 2014 in Lisbon, Portugal, continued a series of events initiated in 2008, capturing the advances on special circuits, electronics, and micro-electronics on both theory and practice, from fabrication to applications using these special circuits and systems. The topics cover fundamentals of design and implementation, techniques for deployment in various applications, and advances in signal processing.

Innovations in special circuits, electronics and micro-electronics are the key support for a large spectrum of applications. The conference is focusing on several complementary aspects and targets the advances in each on it: signal processing and electronics for high speed processing, micro- and nano-electronics, special electronics for implantable and wearable devices, sensor related electronics focusing on low energy consumption, and special applications domains of telemedicine and ehealth, bio-systems, navigation systems, automotive systems, home-oriented electronics, bio-systems, etc. These applications led to special design and implementation techniques, reconfigurable and self-reconfigurable devices, and require particular methodologies to be integrated on already existing Internet-based communications and applications. Special care is required for particular devices intended to work directly with human body (implantable, wearable, eHealth), or in a human-close environment (telemedicine, house-oriented, navigation, automotive). The mini-size required by such devices confronted the scientists with special signal processing requirements.

We take here the opportunity to warmly thank all the members of the CENICS 2014 Technical Program Committee, as well as the numerous reviewers. The creation of such a high quality conference program would not have been possible without their involvement. We also kindly thank all the authors who dedicated much of their time and efforts to contribute to CENICS 2014. We truly believe that, thanks to all these efforts, the final conference program consisted of top quality contributions.

Also, this event could not have been a reality without the support of many individuals, organizations, and sponsors. We are grateful to the members of the CENICS 2014 organizing committee for their help in handling the logistics and for their work to make this professional meeting a success.

We hope that CENICS 2014 was a successful international forum for the exchange of ideas and results between academia and industry and for the promotion of progress in the field of circuits, electronics and micro-electronics.

We hope Lisbon provided a pleasant environment during the conference and everyone saved some time for exploring this beautiful city.

## **CENICS 2014 Chairs:**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

# **CENICS 2014 Research/Industry Chairs**

Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India

# **CENICS 2014 Industry Liaison Chairs**

Falk Salewski, Muenster University of Applied Sciences, Germany

# **CENICS 2014 Publicity Chair**

Sandra Sendra Compte, Universidad Politécnica de Valencia, Spain

CENICS 2014 Special Area Chairs Formalisms Peeter Ellervee, Tallinn University of Technology, Estonia Application-oriented Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain Sensors

Yulong Zhao, Xi'an Jiaotong University, China

# **CENICS 2014**

# Committee

## **CENICS Advisory Chairs**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

## **CENICS 2014 Research/Industry Chairs**

Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India

## **CENICS 2014 Industry Liaison Chairs**

Falk Salewski, Muenster University of Applied Sciences, Germany

## **CENICS 2014 Publicity Chair**

Sandra Sendra Compte, Universidad Politécnica de Valencia, Spain

## **CENICS 2014 Special Area Chairs**

## Formalisms

Peeter Ellervee, Tallinn University of Technology, Estonia

#### **Application-oriented**

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain

#### Sensors

Yulong Zhao, Xi'an Jiaotong University, China

#### **CENICS 2014 Technical Program Committee**

Amr Abdel-Dayem, Laurentian University, Canada Amir Shah Abdul Aziz, TM Research & Development, Malaysia Adel Al-Jumaily, University of Technology, Sydney Said Al-Sarawi, The University of Adelaide, Australia Mohammad Amin Amiri, Iran University of Science and Technology, Iran Lotfi Bendaouia, ETIS-ENSEA, France Yngvar Berg, Vestfold University College, Norway Madhu Bhaskaran, RMIT University, Australia Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Javier Calpe, University of Valencia, Spain James M. Conrad, University of North Carolina at Charlotte, USA Jose Carlos Meireles Monteiro Metrolho, Polytechnic Institute of Castelo Branco, Portugal David Cordeau, University of Poitiers, France Marc Daumas, Université de Perpignan, France Javier Diaz-Carmona, Technological Institute of Celaya, Mexico Gordana Jovanovic Dolecek, Institute INAOE - Puebla, Mexico Peeter Ellervee, Tallinn University of Technology, Estonia Ykhlef Faycal, Centre de Développement des Technologies Avancées, Algeria Sérgio Adriano Fernandes Lopes, Universidade do Minho, Portugal Francisco V. Fernández, IMSE, CSIC and University of Sevilla, Spain Joaquim Filipe, EST Setubal, Portugal Luis Gomes, Universidade Nova de Lisboa, Portugal Petr Hanáček, Brno University of Technology, Czech Republic Martin Horauer, University of Applied Sciences Technikum Wien, Austria Chun-Hsi Huang, University of Connecticut, U.S.A. Wen-Jyi Hwang, National Taiwan Normal University, Taiwan Emilio Jiménez Macías, University of La Rioja, Spain Anastasia N. Kastania, Athens University of Economics and Business, Greece Kenneth Blair Kent, University of New Brunswick, Canada Tomas Krilavicius, Vytautas Magnus University - Kaunas & Baltic Institute of Advanced Technologies -Vilnius, Lithuania Junghee Lee, Georgia Institute of Technology, USA Kevin Lee, Murdoch University, Australia Hongen Liao, Tsinghua University, China Diego Liberati, National Research Council of Italy, Italy Alie Eldin Mady, University College Cork (UCC) - Cork, Ireland Cesare Malagu', University of Ferrara and Istituto di acustica e sensoristica Orso Maria Corbino CNR-**IDASC**, Italy José Carlos Metrôlho, Instituto Politécnico de Castelo Branco, Portugal Yoshikazu Miyanaga, Hokkaido University, Japan Bartolomeo Montrucchio, Politecnico di Torino, Italy Adrian Muscat, University of Malta, Malta Arnaldo Oliveira, Universidade de Aveiro, Portugal Adam Pawlak, Silesian University of Technology - Gliwice, Poland George Perry, University of Texas at San Antonio, USA Angkoon Phinyomark, Prince of Songkla University, Thailand Eduardo Correia Pinheiro, Instituto de Telecomunicações - Lisboa, Portugal Anton Satria Prabuwono, Universiti Kebangsaan Malaysia, Malaysia Vladimir Privman, Clarkson University - Potsdam, USA Càndid Reig, University of Valencia, Spain Marcos Rodrigues, Sheffield Hallam University, U.K. Falk Salewski, Muenster University of Applied Sciences, Germany Arvind K. Srivastava, NanoSonix Inc., USA Ivo Stachiv, National Chung-Cheng University / Institute of Physics - Czech Academy of Sciences, Taiwan / & Czech Republic Ephraim Suhir, University of California – Santa Cruz, USA Ivo Stachiv, Institute of Physics - Academia Sinica, Taiwan João Manuel R. S. Tavares, Universidade do Porto, Portugal

Felix Toran, European Space Agency, Germany Francisco Torrens, Institut Universitari de Ciencia Molecular / Universitat de Valencia, Spain Carlos M. Travieso-González, University of Las Palmas de Gran Canaria, Spain Manuela Vieira, UNINOVA/ISEL, Portugal Thomas Webster, Northeastern University, USA Chin-Long Wey, National Central University, Taiwan Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India Jianhua (Joshua) Yang, Hewlett Packard Laboratories - Palo Alto, USA Sergey Y. Yurish, IFSA, Spain David Zammit-Mangion, University of Malta – Msida, Malta

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

# **Table of Contents**

| Novel High Speed and Robust Ultra Low Voltage CMOS NP Domino Carry Gate<br>Abdul Wahab Majeed, Halfdan Solberg Bechmann, and Yngvar Berg                                                                    | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Simultaneous Measurement of Temperature and Expansion on Radio Frequency Power Electronic Components<br>Eric Joubert, Olivier Latry, and Jean-Philippe Roux                                                 | 7  |

| Robustness Study of SiC MOSFET Under Harsh Electrical and Thermal Constraints<br>Safa Mbarek, Pascal Dherbecourt, Olivier Latry, Francois Fouquet, Dhouha Othman, Mounira Berkani, and<br>Stephane Lefebvre | 11 |

| A Log-Tool Suite for Embedded Systems<br>Harald Schuster, Martin Horauer, Michael Kramer, Heinz Liebhart, and Josef Buger                                                                                   | 16 |

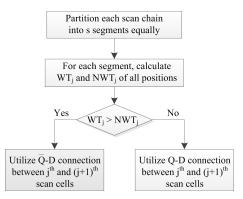

| Scan-shift Power Reduction Based on Scan Partitioning and Q'-D Connection <i>Tiebin Wu, Li Zhou, and Hengzhu Liu</i>                                                                                        | 21 |

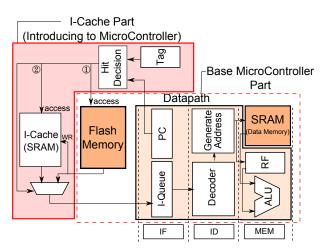

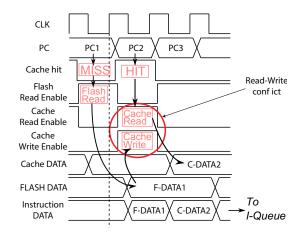

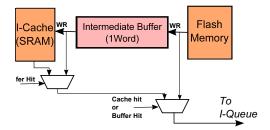

| A Study of Transparent On-chip Instruction Cache for NV Microcontrollers<br>Dahoo Kim, Itaru Hida, Eric Fukuda, Tetsuya Asai, and Masato Motomura                                                           | 26 |

# Novel High Speed and Robust Ultra Low Voltage CMOS NP Domino Carry Gate

Abdul Wahab Majeed\*, Halfdan Solberg Bechmann<sup>†</sup>, Yngvar berg<sup>‡</sup>

Departments of Informatics

University of Oslo, Oslo, Norway

\*Email: abdulwm@ifi.uio.no

<sup>†</sup>Email: halfdasb@ifi.uio.no

<sup>‡</sup>Email: yngvarb@ifi.uio.no

Abstract—In this paper, a novel design of an Ultra Low voltage Carry Gate shall be presented. The main objective is to target the robustness of the presented ciruits. We shall also imply as to what extent these circuits can be improved and what their benefits, compared to conventional topologies, are. The design presented, compared to a conventional CMOS carry gate, is area efficient and high speed. The relative delay of a ULV carry gate lies at less than 3% compared to conventional CMOS carry gate. The circuits are simulated using the TSMC 90nm process technology and all transistors are of the Low Threshold Voltage (lvt) type. *Index Terms—ULV; Carry Gate; NP domino.*

# I. INTRODUCTION

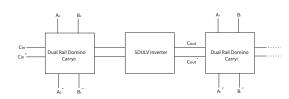

As the semiconductor industry grows, the demand for Ultra Low Voltage (ULV) circuits is increasing. These circuits are being implemented in VLSI where different kind of functions are combined on one chip. The Arithmetic Logic Units (ALU)s are one of the many circuits that are implemented in the VLSI chips. Since an adder is an important part of the ALU, the speed of the adder used, is important for the ALU performance. The speed of the adder is determined by the propagation delay of the carry chain. Although high speed conventional carry circuits like Carry Look Ahead, Dual rail domino carry, CPL, etc., are well established design topologies, their performance at ULV suffers from degradation [1]. Several approaches are proposed for the improvement of performance [2][3] but the design presented in this paper is influenced by [4]. This paper shall present a new high speed NP domino ULV carry design. To highlight the improvement, the results shall be compared to conventional domino design such as Dual Rail Domino carry. Both the carry circuits are implemented in a 32-bit carry chain in order to show as to what extent one is better than the other, regarding their speed and power.

Section I-A presents a general introduction to the ULV circuits presented in [5]. Section II presents different configurations of ULV carry designs and gives an explanation on how it works. Section III presents the performance of the proposed ULV carry gate compared to the conventional carry gate.

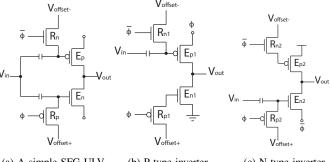

#### A. ULV Inverter

1) Evaluation and Precharge Phase: A simple ULV inverter model is presented in the Figure 1a. A ULV Semi-Floating gate circuit design consists of two phases, an evaluation phase, determined by the evaluation transistors  $E_n$  and  $E_p$ , and a precharge phase determined by the precharge transistors  $R_n$  and  $R_p$ . As seen in the Figure 1a  $\overline{\phi}$  is applied to  $R_n$  and

(a) A simple SFG-ULV (b) P-type inverter (c) N-type inverter inverter

$\phi$  is applied to  $R_p$ . In such a circuit, the precharge phase occurs when  $\phi=0$  and the circuit enters evaluation phase when  $\phi=1$ . During the precharge phase, the input floating nodes are charged to a desired level i.e logical 1 or  $V_{DD}$  for the  $E_n$ floating gate and logical 0 or Ground (GND) for the  $E_p$  floating gate. No input transition occurs during the precharge phase. However, once the clock shifts from logical 0 to 1 and has reached a stable value of 1, an input transition may occur, which determines the logical state of the circuit's output. We can configure the circuit in an NP domino fashion by engaging  $E_n$  to  $\overline{\phi}$  (where  $\overline{\phi}=1$  during the precharge phase) and  $E_p$  to  $V_{DD}$ . Such a configuration yields a precharge level of logical 1 and is called an N-type circuit. On the other hand, if we engage  $E_n$  to GND and  $E_p$  to  $\phi$  we can obtain a precharge level of 0. Such a configuration is called a P-type circuit.

Considering the example of N-type inverter, we know that the output of N-type is precharged to 1. Once  $\phi$  shifts from 0 to 1, circuit enters the evaluation phase. During the evaluation phase, there are two possible situations. If no input transition occurs, the output shall remain unchanged and hold its value to 1. Indicating that no work is to be done. However, if an input transition occurs and input is brought to 1 the  $E_{n2}$  shall be turned on and the output shall be brought to logical 0 or close to 0. This indicates that the only work to be done during the evaluation phase is to bring the output from 0 to 1 when an input transition occurs.

We have seen that the only work that is to be done, during the evaluation phase, is to bring the output to the logical 0 when an input transition occurs. This suggests that  $E_{p2}$  does

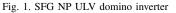

Fig. 2. 1 bit full adder

not require an input transition at any stage. Therefore, we can remove the input capacitor of  $E_{p2}$ . Such a configuration can be called pseudo SFG ULV inverter and is shown in Figure 1c. An equivalent P-type Pseudo SFG ULV inverter is shown in Figure 1b. This will lead to load reduction and hence higher speed. However, we may encounter some robustness issues with respect to noise margin due to leakage current.

#### II. METHODS

$$C_{out} = A \cdot B + (C_{in} \cdot (A \oplus B)) \tag{1}$$

The output of a carry circuit is generated using two inputs and a carry bit from the previous stage, if available (carry bit at the least significant bit is always zero so it has no previous carry), as shown in figure 2. Equation (1) shows an arithmetic approach to carry generation where A and B is the input signal and  $C_{in}$  is the carry bit from the previous stage. There are two parts of this equation, one is generated internally,  $A \cdot B$ , and can be called carry generation (CG), the other one is dependent on the carry bit from the previous stage,  $(C_{in} \cdot (A \oplus B))$ , and is known as carry propagation (CP). The speed of any carry chain depends on the second part of this equation, because it has to wait for the carry bit from the previous stage to arrive. Inputs A and B both arives simultaneously at any stage of an N bit carry chain. Most conventional designs use two seperate parts for CG and CP but the design presented in this paper differ from the most designs as it is able to generate both CG and CP by applying all the inputs to a single transistor. This technique is called Multiple valued Logic (MVL) where classical truth value, logical 1 and 0, are replaced by finit or infinite logical values. It has a potential to decrease the chip area and total power dissipation[6].

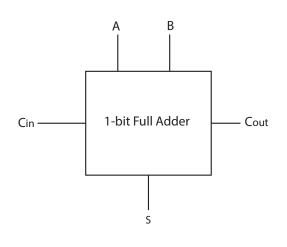

#### A. Non-Differential Carry Gate

The Static Ultra Low Voltage Carry (SULVC) is a modified version of the ULV N-P domino inverter shown in section I-A. The carry circuit uses a keeper as proposed in [5] and

3 capacitors in parallel at the input gate providing the input logic for the circuit. The circuit is designed to make the A and B signal cancel each other out when A and B have contrasting values to allow the carry input signal to determine the carry output in this case. Because of the cancellation requirement between the A and B signals they need to arrive as equally sized rising or falling transitions, this can be acheived by utilizing level-to-edge converters or a logic style with a VDD/2 precharge level.

If both A and B are rising, the floating node will rise causing a falling transition on the carry output of the Ntype circuit regardless of the carry input signal. If they are both falling, the carry input signal can not elevate the floating node voltage enough to cause a transition, leaving the carry output at precharge level. If A and B are not equal, their two transitions cancels each other out and the floating node remains at precharge level until a possible rising edge occurs on Cin. A P-type equivalent of the circuit is shown in Figure 3 (b) where all signals and logic are the inverse of those in the N-type circuit. For both circuits, a transition on the output indicates carry propagation and they can both be characterized as a carry generate circuit corresponding with the truth table shown in Table I, the transition logic for the N-type circuit can be seen in Table II.

During the precharge phase, the voltage level of the floating node is set to ground for the P-type circuit and  $V_{DD}$  for the N-type and can only be changed by the inputs through the capacitors in the evaluation phase. In these circuits, when used in CPAs (Carry Propagate Adder),  $C_{in}$  can arrive later than A and B when the carry bit has to propagate through the chain of carry circuits. This introduces the challenge of keeping the output precharge value during the evaluation phase in case no

TABLE I. TRUTH TABLE FOR A CARRY CIRCUIT

|   | Inpu | Output   |           |

|---|------|----------|-----------|

| А | В    | $C_{in}$ | $C_{out}$ |

| 0 | 0    | 0        | 0         |

| 0 | 1    | 0        | 0         |

| 1 | 0    | 0        | 0         |

| 1 | 1    | 0        | 1         |

| 0 | 0    | 1        | 0         |

| 0 | 1    | 1        | 1         |

| 1 | 0    | 1        | 1         |

| 1 | 1    | 1        | 1         |

TABLE II. TRANSITION TRUTH TABLE FOR N-TYPE SULVC

|              | Inpu | Output   |                      |

|--------------|------|----------|----------------------|

| A            | B    | $C_{in}$ | $\overline{C_{out}}$ |

| $\downarrow$ | ↓    | 0        | 1                    |

| ↓            | ↑    | 0        | 1                    |

| ↑            | ↓    | 0        | 1                    |

| ↑            | 1    | 0        | $\downarrow$         |

| ↓            | ↓    | ↑        | 1                    |

| ↓            | ↑    | ↑        | $\downarrow$         |

| ↑            | ↓    | ↑        | $\downarrow$         |

| ↑            | ↑    | ↑        | $\downarrow$         |

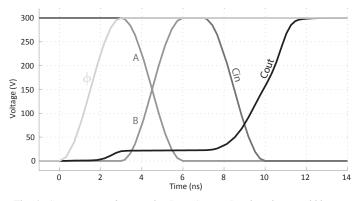

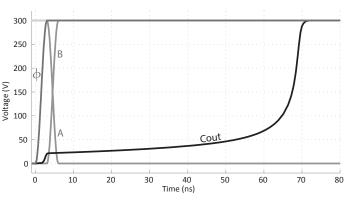

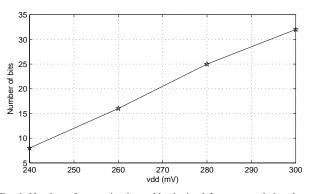

carry signal arrives. As Figure 4 shows, the floating node of the P-type circuit is precharged to 0V. This causes the transistor  $E_{p2}$  in Figure 4 (b) to conduct and the output will drift and may eventually cause an incorrect output value as shown in Figure 5 at 70ns. The drifting effect is countered with the  $K_{n2}$  and  $K_{p2}$  keeper transistors but the effect limits the length of the evaluation pase and therby the number of carry circuits that can be put in a chain and the maximum number of bits an adder based on the circuit can process in one clock cycle. The maximum achieved number of bits acheived varies with the supply voltage as shown in Figure 6 and at 300mV a 32-bit carry chain can be implemented.

The transistor sizing is adjusted to accommodate the change in NMOS/PMOS mobility difference with changed supply voltage. In these simulations the NMOS evaluation transistor size is kept minimum sized and the PMOS evaluation transistor

Fig. 4. Carry input and output for SULVC gate. Supply voltage at 300mV

Fig. 5. Drifting problem of the SULVC output.

Fig. 6. Number of carry circuits or bit obtained from carry chain when supply voltage is varied

length is changed to match the NMOS drive strength.

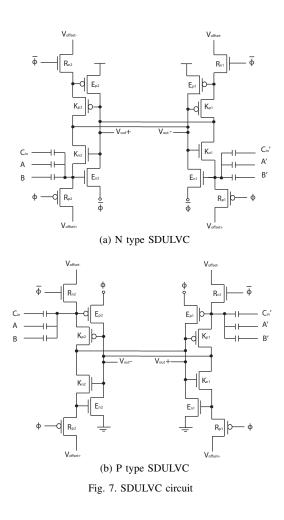

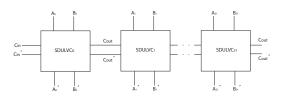

#### B. Differential Carry Gate

In order to overcome the challenges with robustness and drifting of the SULVC circuit, a differential approach is a possible solution. A Static Differential Ultra Low Voltage Carry (SDULVC) as shown in Figure 7 is designed in exactly the same manner as the SULVC, however with differential inputs and outputs. The differential nature of the circuit makes it less prone to drifting and eliminates the need for levelto-edge converters it can be sized to allow a single edge without causing an output transition. The outputs of the proposed circuit are precharged to the same level during the precharge phase, however it yields a differential output during the evaluation phase. So, instead of employing an inverter to obtain the carry bit we can read it from the opposite end of the circuit, i.e. in an N-type SDULVC if inputs A B and C are applied to  $E_{n2}$  output can be read from  $V_{out-}$ . Figure 7 demonstrates the design of an SDULVC circuit. The backgate of the keeper transistors of these circuits are connected to the floating gate to achieve maximum robustness.

$$V_{fg} = V_{initial} + k_{in} \cdot V_{in} \text{ where } k_{in} = \frac{\sum_{i=1}^{n} C_{innHigh_i}}{C_{total}} \quad (2)$$

The variable 'i' in (2) denotes the index of the input and the 'n' denotes fan-in.  $V_{initial}$  is the precharge voltage level of the floating gate.  $C_{inHigh}$  is a combination of input capacitors with a high (rising) input.

Considering an example of an N-type SDULVNC we can calculate the voltage level of the floating gate using (2). We assume that the diffusion capacitance is equal to the input capacitance and that the supply voltage is equal to the input voltage. The load capacitance introduced by the keeper's backgate connection to the floating node should also be considered and is in this paper assumed to be equal to the input capacitor as well.

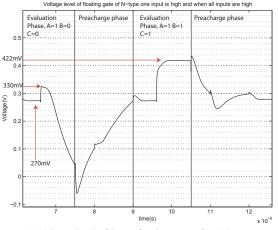

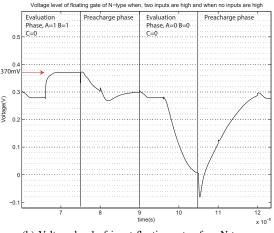

Our calculation in (2) gives us a theoretical idea of the voltage level at  $V_{fg}$  (floating gate voltage). In the real world the capacitance size might not be exactly the same as our assumption and depends on transistor size and many other factors like process variation and mismatch. The simulation results of the voltage levels for the floating gate in the Figure 8 shows that the floating node is precharged to 270mV. Equation (2) yields an analytical result for the floating gate input of 330 mV, 390mV and 450 mV for one, two and three high inputs, respectivly. The simulation results in Figure 8a shows that the voltage level of the floating node gets to 330mV for a single rising input transition and to 420mV when all inputs are high. These results are marginally different from the calculated

(a) Voltage level of input floating gate of an N-type SDULVC/SDULVC when A=1 B=0 and C=0, and when A=1 B=1 C=1

(b) Voltage level of input floating gate of an N-type SDULVC/SDULVC when A=1 B=1 and C=0, and when A=0 B=0 C=0  $\,$

Fig. 9. 32 bit ULV carry chain

values. This is possibly due to the assumptions on capacitance sizes. Figure 8a shows that if only one input gets high, the keeper transistor turns on and discharges the floating node. The reason for this is that the transition at the input, i.e. 60mV, is not sufficient to produce enough current at the output. Figure 8b shows the results for two high inputs and all low inputs.

Fig. 10. Implementation of hybrid Dual rail domino carry

(b) output ULV carry chain P-type

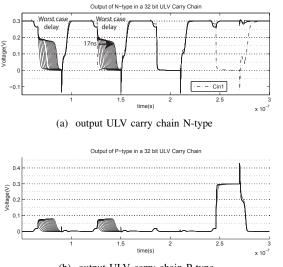

Fig. 11. Simulation result of 32 bit ULV carry chain at a supply voltage of 300mv

#### III. SIMULATION

#### A. 32 bit SDULVC chain

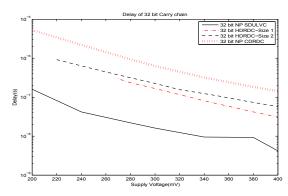

A 32 bit ULV carry chain is implemented using 32 SDULVC circuits connected in a chain or NP domino fashion shown in Figure 9. Figure 11 shows the simulation response of a 32 bit ULV carry chain. The propagtion delay of this carry chain is 17ns. In order to compare the SDULVC to other carry gate topologies, a dual rail domino carry gate designed in a hybrid fashion, i.e. instead of utilizing conventional inverters at the output, the Static Differential ULV inverter presented in [7] and a conventional NP Domino Dual Rail carry is used. Compared to the hybrid dual rail domino carry (HDRDC) chain shown in the Figure 10 the SDULVC chain is almost 10× faster and compared to a Conventional Dual Rail Domino Carry (CDRDC) this is closer to  $35 \times$ . These numbers are based on the propagation delay for the carry bit through the chain, which is 166ns for the hybrid dual rail domino carry and 636ns for the conventional dual rail domino carry, all at 300 mV.

The robustness of the SDULVC can be analyzed by looking at the simulation response shown in Figure 11b. The plot for the worst case delay scenario, i.e. A=1, B=0, C=0, exhibits that due to a delayed carry bit and the early arrival of inputs, A and B, a marginal transition at the output occurs. However, once the carry bit has arrived, the output shifts to its final

#### TABLE III. DIMENSIONS OF HYBRID DUAL RAIL DOMINO CARRY GATE

|        | Supply | Width of dual rail | Length of dual rail | Width of dual rail | Length of dual rail |

|--------|--------|--------------------|---------------------|--------------------|---------------------|

|        | volt-  | domino evaluation  | domino evaluation   | domino precharge   | domino precharge    |

|        | age    | transitor/Width of | transitor/Length of | transitor/Width of | transitor/Length of |

|        | varia- | SDULVN evaluation  | SDULVN evaluation   | SDULVN precharge   | SDULVN precharge    |

|        | tion   | transitor          | transitor           | transitor          | transitor           |

| Size 1 | 270mv- | 4×                 | 3.3×                | 1×                 | 1×                  |

|        | 400mv  |                    |                     |                    |                     |

| Size 2 | 220mv- | 6.67×              | 8.3×                | 3.33×              | $35 \times$         |

|        | 400mv  |                    |                     |                    |                     |

Fig. 12. Delay of 32 bit SDULVC and hybrid dual rail domino at varried supply voltage

value. Average transition at the output for a P-type and N-type SDULVC when waiting for the carry bit is between 70mV and 100mV. This can be seen as a problem for the noise margin and power consumption. The output manages to return to the right final value due to synchronisation of keeper signals with the input. Therefore, the issue of noise margin can be ignored by concluding that the final value can be read at the end of the evaluation phase.

Figure 12 shows the delay of an SDULVC chain compared to an HDRDC and a CDRDC chain. Table III shows that the transistor size has to be increased in order to increase the ON current of the device [8] and be able to decrease the supply voltage for HDRDC. Table IV shows the minimum operating frequency required for the clock to simulate SDULVC, HDRDC and CDRDC at different supply voltages.

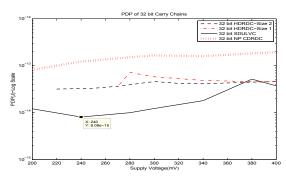

#### B. PDP and EDP of SDULVC chain

PDP charachteristics of a circuit highlights its efficiency with respect to power consumtion. A low PDP means a more

| Supply | $f_{min}$ for | $f_{min}$ for | $f_{min}$ for | $f_{min}$ for |

|--------|---------------|---------------|---------------|---------------|

| Volt-  | SDULVC        | HDRDC-Size    | HDRDC-Size    | CDRDC         |

| age    | (MHz)         | 1 (MHz)       | 2 (MHz)       |               |

| (mV)   |               |               |               |               |

| 200    | 1.6           | -             | -             | 0.08          |

| 220    | -             | -             | -             | -             |

| 240    | 3.125         | -             | -             | 0.217         |

| 250    | -             | -             | 0.83          | -             |

| 270    | -             | 1.66          | 1.225         | -             |

| 280    | 6.25          | -             | -             | 0.5           |

| 300    | 8.33          | 2.3           | 2             | 0.769         |

| 320    | -             | -             | 2.27          | -             |

| 340    | 16.66         | 5.5           | 3.33          | 1.562         |

| 380    | 21            | 10            | 5.55          | 2.5           |

| 400    | 23.8          | 60            | 7.692         | 3.33          |

TABLE IV. TABLE IV: MINIMUM CLOCK OPERATING FREQUENCY FMIN REQUIRED BY THREE TOPOLOGIES

Fig. 13. PDP of 32 bit carry chains

Fig. 14. EDP of 32 bit carry chains

energy efficient circuit. Although the ULV circuits presented in this paper are power hungry, it still manages to maintain its PDP at approximately the same level as conventional circuits where the power consumption is lower. The average power of the HDRDC and the SDULVC is  $0.347\mu W$  and 1.28nWrespectively at a supply voltage of 300 mV. This indicates that the power consumption of HDRDC is up to  $3\times$  better than ULV circuits. However, at the same supply voltage the ULV circuit is  $10\times$  faster than the HDRDC. Therefore, the ULV circuits are still more energy efficient. Figure 13 shows PDP of three different 32 bit carry chain topologies at varied supply voltage. The minimum energy point of the 32 bit SDULVC carry chain is found at 240 mV.

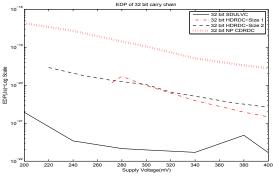

Another important charachteristic of any circuit is EDP. It demonstrates enhanced speed of any circuit with respect to its energy efficiency. It is obvious that circuits with better propagation delay shall stand out in this characteristic. Figure 14 shows the EDP of three carry chains and the evident performance advantages of SDULVC circuits.

#### IV. CONCLUSION

In this paper, a new ULV carry circuit has been presented and performance enhancements have been demonstrated. The ULV carry circuits are better than conventional topologies in both speed and energy efficiency, shown by comparing the SDULVC to the HDRDC and CDRDC circuit topologies. A credible conclusion is that a static differential dynamic ULV carry circuit is a favorable choice when speed and robustness at low voltages are important.

#### REFERENCES

- M. Alioto and G. Palumbo, "Impact of supply voltage variations on full adder delay: Analysis and comparison," *Very Large Scale Integration (VLSI) Systems, IEEE Transactions on*, vol. 14, no. 12, pp. 1322–1335, 2006.

- [2] —, "Very high-speed carry computation based on mixed dynamic/transmission-gate full adders," in *Circuit Theory* and Design, 2007. ECCTD 2007. 18th European Conference on, 2007, pp. 799–802.

- [3] Y. Berg and O. Mirmotahari, "Ultra low voltage and high speed cmos carry generate circuits," in *Circuit Theory and Design*, 2009. ECCTD 2009. European Conference on, 2009, pp. 69–72.

- [4] Y. Berg, "Ultra low voltage static carry generate circuit," in Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on, 2010, pp. 1476–1479.

- [5] Y. Berg and O. Mirmotahari, "Ultra low-voltage and high speed dynamic and static cmos precharge logic," in *Faible Tension Faible Consommation (FTFC), 2012 IEEE*, june 2012, pp. 1–4.

- [6] Y. Berg, S. Aunet, O. Naess, O. Hagen, and M. Hovin, "A novel floating-gate multiple-valued cmos full-adder," in *Circuits and Systems*, 2002. ISCAS 2002. IEEE International Symposium on, vol. 1, 2002, pp. I–877–I–880 vol.1.

- [7] Y. Berg and O. Mirmotahari, "Static differential ultra lowvoltage domino cmos logic for high speed applications."

- [8] M. Alioto, "Ultra-low power vlsi circuit design demystified and explained: A tutorial," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 59, no. 1, pp. 3 –29, jan. 2012.

# Simultaneous Measurement of Temperature and Expansion on Radio Frequency Power Electronic Components

Eric Joubert, Olivier Latry GPM UMR 6634 Université de Rouen - France eric.joubert@univ-rouen.fr olivier.latry@univ-rouen.fr

*Abstract*—This paper presents a new approach for measuring physical variables on micro-electronic components. An optical system is used to simultaneously quantify the surface temperature of a component and its expansion. This double acquisition is achieved by a Michelson interferometer coupled with a Charge Coupled Device (CCD) line device. To validate this method, the temperature measurements were directly compared with the results obtained by an infrared camera and by a measurement of variation of I(V). The displacement measurements were compared with those obtained by a laser 3D vibrometer, whose physical principle is completely different. Consistent results were obtained regarding the different techniques.

Keywords-thermal measurement; laser; electronic components.

#### I. INTRODUCTION

Modern telecommunications and radar systems require the development of increasing Radio Frequency (RF) power. The new generation of electronic power transmitters uses solid state technology (GaAs, LDMOS, GaN) transistors. To properly manage parameters, such as size, weight and cooling requirements, these components have to improve many other parameters, such as electrical efficiency and power density while maintaining a high level of reliability and miniaturization. Because of these constraints, the behavior of these components that are subject to high thermal stress, is increasingly difficult to characterize. There is currently a high demand to fully understand the impact of thermal parameters on overall performance and lifetime. This is why it has become essential to develop measurement tools that characterize these kinds of phenomena.

In literature, many technologies are very efficient to extract different types of parameters separately. Some methods use a measurement of  $V_{be}$  on a small cycle of the signal to extract the average junction temperature [2]. Others place thermal sensors directly in power Print Circuit Board [5]. The micro-Raman spectroscopy combined with infrared technology provides accurate thermal values [1][7]. Using nematic liquid crystal thermography is very efficient for specific emissive components [4]. Thermoreflectance imaging using specific wavelengths measurement allows thermal changes measurements over large time scales [8]. It is possible to reach very high thermal resolutions with an

Jean-Philippe Roux CEVAA - France jp.roux@cevaa.com

Optical Time Domain Reflectometer coupled with a Michelson interferometer [3]. Finally, speckle interferometry provides data on the physical deformation of a component subjected to thermal stress [6].

In this state of the art, all the methods aim at providing unique physical data for a device. However, integrating temperature and expansion makes it possible to estimate the dilatation factor of the constitutive material of a power electronic device. In fact, this parameter provides valuable information in the study of the degradation of electronic component under stress.

This paper also suggests a method for measuring simultaneously temperature and expansion of microelectronic components. The first part presents the optical structure of our bench and the physical data measured to estimate temperature and expansion. The second part describes the particular optical calibration process. The third part details the specific sensor we used to transfer the interferometric information to the acquisition device. At last, test devices and results obtained are proposed and discussed in relation with other thermometric/expansion methods.

#### II. OPTICAL SYSTEM

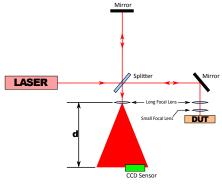

The system is based on a Michelson interferometer [6], as presented in Figure 1. The beam produced by a laser is split into two separate paths. The measuring path uses the device under test and the reference path is reflecting on a plane mirror. The interferometric pattern, which is the sum of the two branches, passes thereafter through a long focal lens.

Figure 1. Structure of the interferometer.

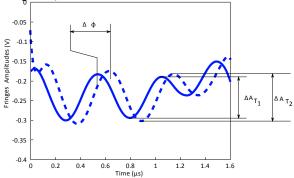

A Charge Coupled Device analyses the interference pattern, contrary to conventional interferometers that are using a single point measurement. This feature allows to measure two parameters: the displacement and amplitude of the interference fringes. This makes our method completely unique. Thereafter, these parameters are used to determine respectively the expansion and temperature of the component (see Figure 2).

Figure 2. Fringes changes according to expansion and temperature.

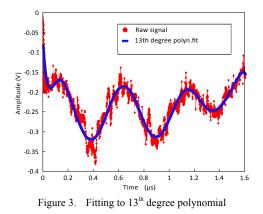

The distance between the lens and the sensor is adjusted to take the inter-pixel distance into account. A polynomial interpolation is applied to ensure an efficient filtering of the recovered electrical signal (see Figure 3).

#### *A. Temperature measurement*

The temperature is calculated from the amplitude of the interference fringes obtained. Indeed, the reflectance of the material depends on the temperature encountered through its refractive index according to the equation:

$$R(T) = \left(\frac{n_1 - n_2(T)}{n_1 + n_2(T)}\right)^2 \tag{1}$$

where R(T) denotes the reflection coefficient,  $n_1$  and  $n_2$  are the refractive indices of the materials 1 and 2, respectively. Under these conditions, the intensity for each point of the interference pattern (perpendicular to the optical axis z) is affected by the reflection coefficient:

$$I(x,y) \propto A_{1}^{2}(x,y) + R(T) \cdot A_{2}^{2}(x,y) + 2 \cdot \cdot A_{1}(x,y) \cdot \sqrt{R(T)} \cdot A_{2}(x,y) \cdot \cos(\phi_{2}(x,y) - \phi_{1}(x,y))$$

(2)

where  $\phi l(x, y)$  and  $\phi 2(x, y)$  are the local phases of the waves 1 and 2. The amplitude of the interference (the third term of equation 2) is increasing linearly as a function of the reflection coefficient. By measuring changes of contrast of the interference fringes, or measuring the peak to peak values of the fringes, it is also possible to measure the temperature of the component.

#### B. Expansion measurement

The expansion of the component is determined by measuring the displacement of the fringes of the interference pattern. The phase shift induced by the expansion causes a shift in the interference pattern. The circular fringes move outwardly in the case of expansion and inwardly in the case of a contraction.

For a contraction of  $10\mu m$ , the fringes move a few millimeters. Simultaneously, these fringes have their width changed. The expansion can either be determined by observing the displacement or the width of the fringes.

#### III. CALIBRATION METHOD

The system is calibrated with a raw wafer of silicon. The ideal surface of the material allows an easy implementation of the interferometer system.

The wafer is thermally excited by a Peltier module. The temperature induced by this module is directly measured by the voltage Up at its terminals. Indeed, the temperature difference  $\Delta T$  provides by the Peltier module is in relation with its electrical characteristics according to the equation:

$$\Delta T = \frac{U_p - n.R.I_p}{n.\alpha} \tag{3}$$

where *n* is the number of cells in the module, *R* the resistivity of the module, *Ip* the module current and  $\alpha$  the Seebeck coefficient.

The expansion is calibrated by comparing it with that obtained by an industrial laser Doppler vibrometer at a frequency in convenience with the characteristics of the interferometer (frequency not exceeding a few Hz).

#### IV. ACQUISITION

During the thermal excitation, the cross-sections of interference pattern are acquired by the CCD line sensor. This sensor transfers 1024 points within a period of 1.7 ms. The analog video signal is converted by a *National Instrument* acquisition unit that has a depth of 24 bits and a

sampling rate of 100kS/s. The recovered data are thereafter processed with Labview [9] to compute displacements and amplitudes of fringes at the maximum rate of the acquisition unit.

Speckle phenomenon in interference pattern brings noise in video signal and reduced overall measurement accuracy. A polynomial fitting of 13<sup>th</sup> degree is first performed to improve the quality of the signal. A detection algorithm follows this filtering to determine the peak amplitude of the fringes. The temperature is determined from this peak after a calibration process.

Measuring displacement of the fringes (and also the expansion of the component) is more complex, because fast moving fringes can be processed as appearing or disappearing. These changes have an important impact on the result. A suitable algorithm allows such a monitoring. The overall process is not real-time: the data are processed after acquisition for avoiding slowing acquisition with computing times.

#### V. TEST DEVICES

Two test components were investigated in order to highlight the characteristics of the temperature measurement on the one hand, and of the expansion on the other hand.

The component used for temperature measurements is an integrated preamplifier that was opened by laser ablation and chemical attack. This component comprises an ElectroStatic Discharge (ESD) diode that allows in situ measurement of the component temperature. As it is a complex integrated circuit, an externally controlled Peltier cell [10] was used to heat the component.

The component used for the expansion action was a 14x3cm aluminum blade simulating a real board used in radar systems. The size of this board allowed to use a miniature shaker.

#### VI. RESULTS

#### A. Temperature

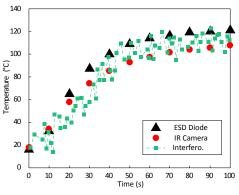

The temperature measurements on the test component were validated by two measurement systems: an internal measurement with an ESD diode and a measurement carried out by a dedicated Infra-Red camera.

The ESD diode was polarized to a constant current so as to generate a voltage near the threshold voltage. This bias point limits the self-heating of the diode. Locally, the changes in the voltage V are a quasi-linear function of the temperature T in ° C:

$$T = 1280,6 \text{ x V} - 156,43 \tag{4}$$

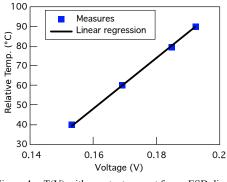

This equation is corresponding to the calibration curve on the real component, obtained by comparison with a thermocouple (see Figure 4).

Figure 4. T(V) with constant current for an ESD diode

The second set of measurements was performed using an infrared camera for electronic components. The camera was corrected for emissivity at 20°C.

The interferometer measurement was not performed simultaneously due to the lack of space above the device under test. However, the physical conditions (heat rise) were identical.

Figure 5. Result for a long temperature rise with the three methods

These results show a good correspondence between the three techniques, even if the interferometer has a measurement uncertainty (see Figure 5). These errors  $(\pm 10^{\circ}C)$  are due to measurement conditions that were not optimal on the component under test. A better mechanical isolation should limit these effects. Moreover, one must keep in mind that the detection area is very small for the interferometer, whereas detection areas for the other techniques are larger. A larger area obviously brings an averaging effect. The error of  $15^{\circ}C$  at 100s between IR camera and ESD diode is due to an emissivity compensation problem. This gap on the infrared camera could be removed efficiently by using black paint on the component to compensate the emissivity of the emitting surface.

#### B. Expansion

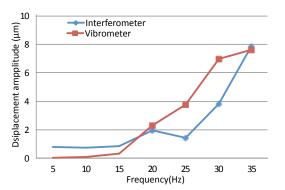

The goal here was to measure the ability of the interferometer to reach high frequencies and thus to provide a possible recovery operation range with Polytech vibrometer PSV400.

Figure 6. Comparison of the amplitudes measured with the two systems

Comparative measurements were made sequentially to solve practical issues of space above the component to be tested. For each measurement, conditions were the same: aluminum board was subjected to a shaker controlled by 1KHz sine signal bursts whose repetition frequency varied between 5Hz and 35Hz. The resulting signals were processed by time FFT and compared in Figure 6.

This figure shows the results for the two systems are quite consistent with the curve of mechanical response of the shaker. The average uncertainty of the vibrometer depends on working frequency and is about 1% on the frequency range 5hz-35Hz. Beyond this overall trend, both techniques show very similar results, despite very important differences in their physical principle. In fact, the interferometer is limited at high frequencies by the sampling due to CCD sensor. In the same time, the Doppler vibrometer principle implies that a minimum frequency is required for the detection to take place.

#### VII. CONCLUSION

The bench that we built enables to simultaneously acquire surface temperature and expansion of an electronic component. These measurements are made on the fringes of the interference pattern resulting from a Michelson interferometer.

In this pattern, two important parameters are extracted. On the one hand, the displacement of the fringes relative to the center of the interference pattern provides useful information regarding the thermal expansion of the component. On the other hand, the variation of the intensity of the fringes is due to changes in reflectance of the observed surface. These changes are due to the variations in the refractive index as a function of temperature. The intensity of the fringes therefore indirectly provides the temperature of the component. Our method allows to de-correlate two quantities linked physically. This makes it possible to evaluate specific mechanical parameters of the component like its expansion coefficient.

This simultaneity is obtained using a CCD line sensor. Adjusting the position sensor and optimally setting the focusing lens system allow adaptation to different contexts. Our system was compared to other systems for measuring temperature and another system for measuring dynamic displacement. This separated temperature/ expansion comparison was inevitable because unlike ours no system can simultaneously measure these parameters. These results show a good correspondence of our method with others, which makes it valid and promising.

#### VIII. ACKNOWLEDGMENTS

The authors wish to thank the cluster Moveo partners, Audacity project and ESP Carnot Institute for the contribution to collaboration GPM/CEVAA.

#### REFERENCES

- R. Aubry et al., "Temperature measurement by micro-raman scattering spectroscopy in the active zone of AlGaN/GaN highelectron-mobility transistors," Eur. Phys. J. Appl. Phys., vol. 27, 2004, pp. 293-296.

- [2] B. M. Cain, P. A. Goud, and C.G. Englefield, "Electrical measurement of the junction temperature of an rf power transistor," IEEE Trans. on Instr. And Meas., vol. 41, 1992, pp. 663-665.

- [3] S. Dilhaire, T. Phan, E. Schauf, and W. Claeys, "Laser probes and methodology for thermal analysis at micrometric scale. Application to microelectronics," . Rev. Gen. Therm., vol. 37, 1998, pp. 49-59.

- [4] C. C. Lee and J. Park, "Temperature measurement of visible lightemitting diodes using nematic liquid crystal thermography with laser illumination," IEEE PhotonicsTechnology Let., vol. 16, 2004, pp. 1706-1708.

- [5] D. Mc Namara, "Temperature measurement theory and practical techniques," Analog Devices, AN-892, 2006.

- [6] K. Nassim, L. Joannes, A. Cornet, S. Dilhaire, E. Schaub, and W. Claeys, "High- resolution interferometry and electronic speckle pattern interferometry applied to the thermomechanical study of a mos power transistor," Microelec. J., vol. 30, 1999, pp. 1125-1128.

- [7] A. Sarua et al., "Combined infrared and raman temperature measurements on device structures,". Mantech Conference Vancouver Canada, 2006, pp. 179-182.

- [8] G. Tessier, S. Holé, and D. Fournier, "Quantitative thermal imaging by synchronous thermoreflectance with optimized illumination wavelengths," Appl. Phys. Let., vol. 78, 2001, pp. 2267-2269.

- [9] A. S. Morris and R. Langari, Measurement and Instrumentation Theory and Application, Elsevier, 2012.

- [10] D. Astrain, J. G. Vian, and J. Albizua, "Computational model for refrigerators based on Peltier effect application," Applied Thermal Engineering, vol. 25, 2005, pp. 3149-3162.

# Robustness Study of SiC MOSFET Under Harsh Electrical and Thermal Constraints

To an in-depth physical failure analysis

Safa Mbarek, Pascal Dherbécourt, Olivier Latry, François Fouquet\* University of Rouen, GPM UMR CNRS 6634 \*IRSEEM, Esigelec Rouen, France mbarek.safa@gmail.com

*Abstract*— The improvement of power conversion systems makes SiC devices very attractive for efficiency, compacity and robustness. However, their behavior in response to short circuit mode must be carefully studied to ensure the reliability of systems. This study deals with a SiC MOSFET. After the description of the component structure and its electrical performances, the paper presents some preliminary results for robustness evaluation in harsh electrical and thermal conditions. Extensive studies are underway to try to correlate the electrical measurements with an in-depth structural analysis.

Keywords-SiC MOSFET; Robustness; Failure analysis; Short-Circuit.

#### I. INTRODUCTION

The SiC powers Metal Oxide Semiconductor Transistors (MOSFET) are very attractive for high temperature application in automotive or aeronautics. The isolated gate and the low drain to source resistance in on-state ( $R_{DSon}$ ) make them ideal for using the MOSFET as a switch for all power electronics applications where efficiency, compacity and robustness are needed.

First, SiC MOSFET had been realized since 1986 [1] even if oxide on SiC were studied before. Many challenges in design have been made in order to expect higher frequencies switching than with Silicon Insulated Gate Bipolar Transistor (IGBT) and with higher operating temperature [7]. Investigations of different types of structures with 4H-SiC or 6H-SiC polytypes have been proposed with different challenges [8] and the vertical power devices double implanted MOSFET (DIMOS) shows very good performances due to its higher bulk mobility [9].

In order to evaluate the robustness of this type of MOSFET, several tests are possible. High temperature gatebias (HTGB) and high temperature reverse-bias (HTRB) tests are common qualification tests for discrete semiconductor devices [10] however the short-circuit test [4][6][11] is one of the most used to evaluate the ruggedness of power devices during conduction. By using this test on a commercial 1.2 kV SiC Power MOSFET, the thermal instability and the electro-thermal behaviour are investigated in [11] by the mean of a state-of-art IR thermographic set-up. Dhouha Othman, Mounira Berkani, Stéphane Lefebvre SATIE UMR CNRS 8029 ENS Cachan Cachan, France

Othman et al. [4][6] present a comparison study on performances, reliability and robustness between SiC MOSFET and JFET devices. The aim of the studies is to evaluate the abilities and effects of each technology on the conception of power converter for avionic applications and to analyse their capability to withstand with harsh electrical constrains. The purpose of this paper is to present preliminary experimental results that could help to understand impact of the physical failure on the performance of the SiC MOSFET. First, the DIMOS is characterised in short circuit test. Then, two failure mechanisms are put in light with microstructural analysis.

#### II. COMPONENT UNDER TEST

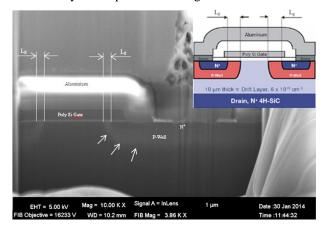

The device under test (DUT) is a 1.2 kV SiC-MOSFET with continuous drain current  $I_{Dmax}$  equal to 24 A at 25 °C. The DUT is a vertical DIMOS transistor and its structure for an elementary cell is presented in Figure 1.

Figure 1. Structure investigation of DUT.

The Poly-Silicon Gate is isolated from the lateral channel with a thin oxide layer and the channel length is Lg. The Drain terminal is connected to the bottom of the device and is coupled to the channel through a drift layer that contributes to the on-state resistance and allows to apply large voltages between Drain and Source during off-state. The other two terminals are fixed on the top of the device and the Source electrode, which is made of Aluminum, entirely covers the top face except on the Gate bonding wire pad.

Finally, the die is brazed on a Copper base plate that carries out the heat preventing from over self-heating during electrical conduction. The brazing, an alloy of Tin, Silver and Antinomy, is limited to a maximum operating temperature of 260°C.

As our main goal is to correlate the physical failure analysis of the DUT and the analysis of its cross section structure with the help of Scanning Electron Microscopy (SEM) after Focused Ion Beam (FIB) sample etching, the first step is to make sure that the depackaging process has no impact on the DUT electrical behavior. In order to verify this point, we have compared current-voltage (IV) characteristics before and after opening.

#### III. IVT CHARACTERIZATION

The static behavior of the transistor is studied over the recommended range of operating temperature according to the constructor datasheet (from -55 °C to +135 °C). Our study is restricted to the evolution of the drain current  $I_D$  depending on temperature variation, reflecting the behavior of the transistor.

To perform the current-voltage-temperature (IVT) measurements while providing thermal stabilization of the DUT, three experimental means have been implemented. For the negative temperatures, a cold forced air system is used; for positive and high temperatures, a Peltier module and a plate heating resistor are required. A thermocouple sensor, positioned as close to the base plate of the DUT as possible, controls its temperature. This setup provides a good accuracy and a satisfactory stability during measurements.

Pulsed mode is suitable to avoid any self-heating of the DUT during the static measurements. To satisfy this requirement, the pulse drain temporally includes the gate pulse. The pulse drain duration is fixed to 3 microseconds, with a duty cycle equal to 0.15%.

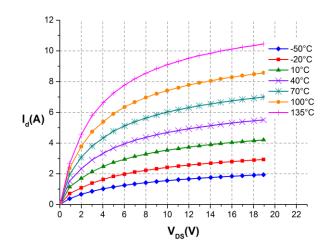

The output curves  $I_D$  (V<sub>DS</sub>, T) in Figure 2 are plotted for a low gate voltage V<sub>GS</sub> equal to 10V over a temperature range extending from -50 °C to 135 °C showing a steady increase in the drain current with the temperature increase.

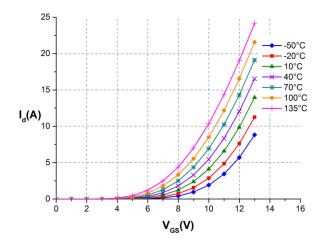

The input curves  $I_D$  (V<sub>GS</sub>, T) in Figure 3 are plotted for the same values of temperature, and for an output voltage V<sub>DS</sub> equal to 18 V. The measurements suggest, as expected, a significant reduction in the threshold voltage V<sub>th</sub> as a function of temperature.

Figure 2. Output characteric  $I_D\left(V_{DS},T\right)$  for different temperatures with  $V_{GS}=10V.$

Figure 3. Input characteric  $I_D\left(V_{GS},T\right)$  for different temperatures with  $V_{DS}=18V.$

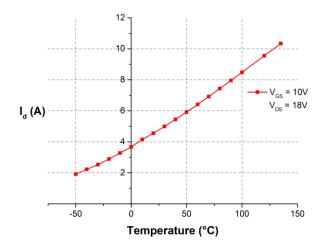

Figure 4. Drain current  $I_{Dsat}$  variation versus the temperature for  $V_{GS}{=}10V$  and  $V_{DS}{=}19V.$

The variation of the drain current is given in Figure 4 in the area of near saturation of the output characteristic, for a gate voltage VGS equal to 10 V and for a drain voltage VDS equal to 19 V.

#### IV. ROBUSTNESS

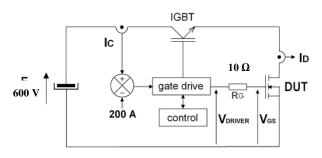

Once the fresh electrical characterization of the devices achieved, a stress campaign is carried out under short circuit tests at room temperature, T = 25 °C. We apply a drain voltage of 600V without any output load. During the short circuit phase, the DUT is maintained in the on-state by applying a gate voltage of 20V and is then switched off by reverse biasing the gate [6]. Dedicated test bench schematic circuit is shown in Figure 5.

Figure 5. Test circuit for short circuit robustness analysis [6].

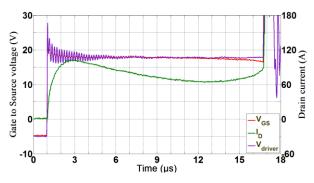

The first step consists in evaluating the energy responsible for the failure over long pulse duration. We applied the short circuit stress to a first component DUT1 for long pulse duration until complete failure. Figure 6 reports waveforms ( $V_{Driver}$ ,  $V_{GS}$  and  $I_D$ ) measured during the short circuit test. The corresponding dissipated energy before failure is about 0.96 J. Results indicate that the device was capable to sustain short circuit tests for a gate drive duration  $t_{SC}$  equal to 16 µs.

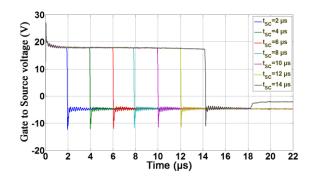

From these observations, we apply the same constraints to a second component DUT2 by applying successive short circuit tests with pulse duration  $t_{SC}$  increased by 2 µs at each test. In these conditions of experimentation, we try to determine the critical energy that is the maximum value of energy controllable by the DUT.

Figure 6. DUT1 : Robustness analysis under long pulse short circuit.

Figure 7. DUT2 : Evolution of gate to source voltage during short circuit tests showing a gate leakage current.

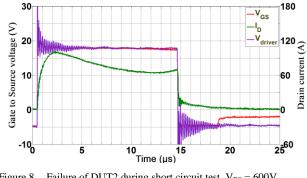

Figure 8. Failure of DUT2 during short circuit test,  $V_{DS}$  = 600V,  $t_{SC}{=}14\mu s,\,T{=}25\ ^{\circ}C.$

As illustrated, Figure 7 shows gate voltage waveforms measured during short circuit operations. The last short circuit stress of  $t_{SC} = 14 \mu s$  applied to DUT2 causes the device failure. Figure 8 reports waveforms ( $V_{Driver}$ ,  $V_{GS}$  and  $I_D$ ) measured during the last short circuit test

#### V. DISCUSSION

#### A. Static I-V characteristics of the DUT

The drain current expression in linear operating region is given by (1), which describes the evolution of  $I_D$  ( $V_{GS}$ ,  $V_{DS}$ ) characteristic. For drain-source voltage ( $V_{DS}$ ) values lower than  $V_{GS}$ - $V_{th}$ , the drain current characteristic is linear, the behavior of the component is then like of a linear voltage-controlled inductance.

$$I_D = \frac{\mu_n W C_{ox}}{L} \cdot \left[ (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(1)

Where W and L are respectively the gate width and the gate length,  $\mu_n$  is the charge-carrier effective mobility and  $C_{ox}$  is the gate oxide capacitance per unit area.

The drain voltage corresponding to saturation mode is defined by the difference between the applied gate voltage and the threshold voltage that is,  $V_{Dsat} = V_{GS}-V_{th}$ . The  $V_{Dsat}$  value read from the output curve of Figure 2, for a temperature of 40 ° C, is equivalent to 10 - 2.9 (V), that to say 7.1V. Beyond this value, for increasing  $V_{DS}$ , the

component works in saturation mode and the current value maintains substantially the  $I_{Dsat}$  value. Then, the current value is independent from  $V_{DS}$  and its expression is given by (2). By experimental measurement, we found a decrease in Vth with temperature over a range from -50 °C to 135 °C. For a given value of  $V_{GS}$ , equation (2) predicts an increase of the saturation current  $I_{Dsat}$ , which is experimentally verified.

$$I_{Dsat} = \frac{\mu_n W C_{ox}}{L} \cdot \left[ \frac{(V_{GS} - V_{th})^2}{2} \right]$$

(2)

More rigorously, we should also take into account the evolution of the mobility  $\mu_n$  which decreases with temperature [5].  $V_{th}$  is also decreasing with temperature; the two variations ( $\mu_n$  and  $V_{th}$ ) have an opposite effect on  $I_{Dsat}$ . Threshold voltage variation is predominant at low gate voltage [2][3], which corresponds to our IVT characterizations as shown in Figures 2 and 3. The opposite behavior occurs for high gate voltage values, i.e.,  $V_{GS}$  equal to 20V corresponding to robustness tests conditions presented in section IV.

#### B. Robustness

It is clearly seen during these robustness tests that the two devices had different failure mechanisms.

As shown in Figure 6, DUT1 fails after thermal runaway by the rapid increase in the drain current due to failure in short-circuit between drain and source. Similar failures were observed for SiC JFET devices for which increase of the temperature beyond the fusion limit of the device metallization was proposed in order to explain failures [4].

However, the transistor DUT2 first turns-off safely and short-circuits current falls down to zero as seen in Figure 8. But, few microseconds after the switch-off, a sudden shortcircuit is observed between gate and source. So, gate failure occurred during transistor's off state after short-circuit but no failure occurred between drain and source electrodes. According to some authors, the gate oxide could be destroyed and the device became uncontrollable [6]. The time between the end of short-circuit and the gate failure may be due to temperature diffusion inside the device, which delay heating on the gate oxide

In Figures 6 and 8, we can clearly notice that a significant leakage current appears about 12  $\mu$ s after the beginning of the short circuit, which seems to be responsible for the devices failures even if the failures seem to be different regarding the gate to source voltage evolution at failure. The decrease of the gate to source voltage during short circuit seems to show degradation between gate and source electrodes during this particular test [4].

#### C. Structural analysis of degradations

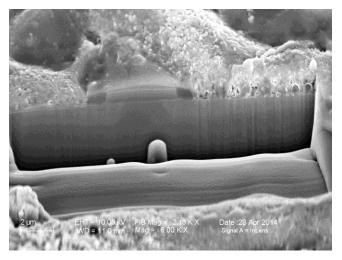

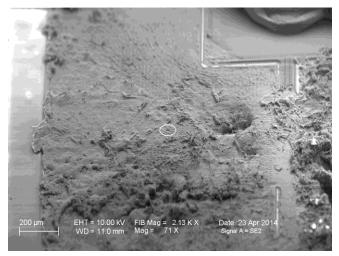

The stressed component DUT1 presenting GDS shortcircuit degradation was unpacked and an example of a FIB cut (Focused Ion Beam) is given in Figure 9.

Figure 9. Material degradation analysis of DUT1.

Analyzing the figure, we could make the following observations:

- We are able to identify the different elements of the structure of the MOSFET,

- The aluminum layer corresponding to the source contact largely melted.

However the reduction of the oxide over the gate polysilicon may be due to the unpacking process; further tests will be performed.

Figure 10. FIB cut location and surface degradation of DUT1.

Regarding the gate oxide, between channel and polysilicon gate, it does not appear to have been damaged by the stress but the FIB cut was performed in a randomly selected location and not where the surface degradations appeared to be the strongest Figure 10.

#### VI. CONCLUSION

A complete thermal IVT characterization has been performed and shows a behavior consistent with the manufacturer's data. Short circuit tests, conducted under extreme conditions, showed a destruction of the two devices under test. However, different failure modes were observed. To better understand the failure mechanisms, current studies are carried out under softer short circuit test in order to highlight significant variations in electrical measurements. Defects generated in the device structure will be located and analyzed by SEM and FIB in the aim to correlate these observations with the electrical measurements.

#### REFERENCES

- [1] Y. Kondo et al., "Experimental 3C-SiC MOSFET," Electron Device Letters, IEEE, vol. 7, no. 7, July 1986, pp. 404–406.

- [2] P. H. Aaen, J. A. Pla, and J. Wood, "Modeling and characterization of RF and microwave power FETs," Cambridge University Press, Ed2007.

- [3] Md. Hasanuzzaman, S. K. Islam, L. M. Tolbert, and M. T. Alam, "Temperature dependency of MOSFET device characteristics in 4H and 6H silicon carbide (SiC)," Solid-Sate Electronics, vol. 48, 2004, pp. 1877-1881.

- [4] D. Othman et al., "Comparison study on performances and robustness between SiC MOSFET & JFET devices – Abilities for aeronautics application," Microelectronics Reliability, vol. 52, 2012, pp 1859-1864.

- [5] B. J. Biliga, "Silicon Carbide Power Devices," North Carolina state university, USA, World Scientific Publishing, Ed 2005.

- [6] D. Othman et al., "Robustness of 1.2 kV SiC MOSFET devices," Microelectronics Reliability, vol. 53, 2013, pp. 1735-1738.

- [7] K. Matocha, "Challenges in SiC power MOSFET design," Solid-State Electronics, vol. 52, no. 10, October 2008, pp. 1631–1635.

- [8] S. Dimitrijev and P. Jamet, "Advances in SiC power MOSFET technology," Microelectronics Reliability, vol. 43, no. 2, February 2003, pp. 225–233.

- [9] V. R. Vathulya and M. H. White, "Characterization and performance comparison of the power DIMOS structure fabricated with a reduced thermal budget in 4H and 6H-SiC," Solid-State Electronics, vol. 44, no. 2, February 2000, pp. 309–315.

- [10] L. Yang and A. Castellazzi, "High temperature gate-bias and reverse-bias tests on SiC MOSFETs," Microelectronics Reliability, vol. 53, no. 9–11, September–November 2013, pp. 1771-1773.

- [11] M. Riccio, A. Castellazzi, G. De Falco and A. Irace, "Experimental analysis of electro-thermal instability in SiC Power MOSFETs," Microelectronics Reliability, vol. 53, no. 9–11, September–November 2013, pp. 1739-1744.

# A Log-Tool Suite for Embedded Systems

Harald Schuster, Martin Horauer, Michael Kramer University of Applied Sciences Technikum Wien Vienna, Austria

e-mail: {schuster, horauer, kramer}@technikum-wien.at

Abstract—Logging is a common method to monitor the operation of a system and to identify failures of services and system components. When developing software for an embedded system there are stricter restrictions that result from the limited hardware resources. The performance of the hardware as well as the available memory is limited. Furthermore, embedded systems are often not accessible for a long period of time. This paper presents tools to improve existing logging methods without compromising existing development flows. Essentially, these tools on one hand transparently pre-process the source code in order to optimize logging instructions and add on the other hand a postprocessing step when analyzing log-files. The presented tools were evaluated by integrating them to an industrial project where they show a significant improvement of the logging performance.

Keywords—Logging; Embedded Systems; Memory Limitation; Log Analysis.

#### I. INTRODUCTION

Electronics paired with software is a key enabler for many modern products and systems. For example, it allows to add new features and functionalities, improve reliability, safety, environmental efficiency, or comfort. At the same time the complexity of these systems is steadily increasing mandating more efforts and new approaches for verification. In practice, various processes and approaches are in use — very common are static analyses, code reviews paired with testing and sometimes even formal methods. For embedded systems this problem is aggravated since usually different environmental conditions, limited controlability, and observability need to be taken into consideration. Thus, rigorous verification is a challenging task that is often limited by economical aspects.

In the field of embedded systems, Embedded Linux gained momentum in recent years due to plummeting costs of available hardware resources, the maturity and the feature rich functionality of the open-source code-base. Here, as with desktop operating systems, logging is a common approach to identify problems of an operational system. Services and applications can write information, warnings and encountered errors to log-files in a chronological fashion. Analyzing these logs can help to identify problems and hint to their sources. Especially when dealing with long-running server applications logging is a common practice. For example, [1] observed that on average common server programs provide one logging instruction every 30 code lines and that 18% of all committed revisions are due to modifications of the respective logging messages. In contrast, to desktop and server systems, memory is still a limiting and costly factor for embedded systems. Hence, for such systems a trade-off between the time a log-file is accumulated, the number of log messages, their frequency and verbosity is important. On one hand, lowering these values is necessary when the amount of available memory is limited -

Heinz Liebhart, Josef Büger Kapsch TrafficCom AG Vienna, Austria e-mail: {heinz.liebhart, josef.bueger}@kapsch.net

this will typically reduce the expressiveness and usefulness of the logs. On the other hand, frequent and verbose log-messages will also impair on the available processing power — the latter being another limited factor.

The main contribution of this paper is to present some tools and a flow that improves the efficiency of existing logging practices. In particular, it optimizes the length, verbosity and performance of the logs without impairing the existing log facilities and requires only a marginal adaption of the development flow. We evaluate our approach using an industrial strength Embedded Linux device that is executing a communication stack used for road-pricing systems.

The remainder of this paper is structured as follows: Section II provides an overview of existing tools and approaches to improve the performance of logging on embedded systems. Then we present our modified tool flow before we provide some implementation details of our LogEnhancer and the LogAnalyzer tools. Afterwards, we describe how we evaluated our tools before we conclude the paper giving an outlook on future directions.

#### II. RELATED WORK

Logging is a common approach to identify problems in a computing solution [2][3][4]. When looking at Linux, for example, multiple different logging methods are available. In the majority of these cases, however, these methods are designed for standard desktop or server systems. Widespread in use are syslog [5] and their forks rsyslog and syslog-ng. Another common logging method is Journal which is included in the system and service manager Systemd. All these systems, however, are not optimized for embedded targets.

For these systems dedicated logging methods exist that improve several aspects when compared to the "standard" methods, cf. [6]. For example, Amontamavut et al. [7] describes a logging mechanism that is optimized for embedded systems with small memory. Their approach is to split the logging mechanism into two parts. One part is executed on the embedded device and sends reduced log messages via Ethernet to a server. The second part is the server and consists of different monitoring and debugging tools. One of these tools is a log analyzer to generate readable log messages. Overall, this approach reduces the log-file size and improves the log performance, however, it requires an active network connection to a remote host when the system is operational; a requirement that rules this approach out for our intended field of application.

Jeong et al. [8] describe a logging mechanism to improve the message throughput and to speed up the latency. They achieved their goals by avoiding the message transfer between the user and the kernel space. The message is stored in a shared memory and forwarded to flash memory or a remote host by a message collector. The developer can use the normal logging API. This changes increases the message throughput but does not affect the log-file size.

#### III. APPROACH

The motivation of our work is to improve the logging functionality of an Embedded Linux device. In particular our approach intends to optimize memory usage and performance without impairing on the existing development process, in particular, how log messages are coded. To that end we first describe existing approaches and development flows used by our industrial partner before we detail our new concept and implementation.

#### A. Status Quo

We implemented and evaluated our approach on code provided by our industrial partner used for embedded devices in the field of road pricing around the globe. In fact, there is already a very large base of devices running in the field; for instance, most commercial road vehicles in the European Union are equipped with these devices. Hence, similar to automotive electronics even small savings have a significant impact on the costs thus simply expanding available resources (computing power, memory size) is critical. Here, next to elaborate testing, logging and off-line analysis of the log-files is a common approach to tackle runtime mis-behavior.

The target employs OpenWRT a Linux distribution for embedded devices as operating system. The application mostly uses C code along with CMake as build system. The employed logging method employs macros to emit log-messages and define statements to set the logging level. The logging levels are ERROR, WARNING, NORMAL, INFORMATION, DEBUG and TRACE. Furthermore, using logging masks it is possible to filter the kind of messages that are logged (e.g., communication related log-messages, layer 2 messages, layer 3 messages).

The source-files consist of roughly 150k lines (counted using the tool cloc) of source-code targeting 3 different targets; Table I lists the log messages found therein separated by their logging level. In total, the source-files hold 2259 log messages; thats on average about one log message every 67 lines of code. Compared to several open-source projects listed in [1] this code contains roughly 2-3 times less log messages. One reason therefore, might be that the code at hand targets an embedded platform, whereas the listed references are aimed at server applications.

TABLE I. LOG MESSAGE STATISTICS

| ſ | LOG_ERR | LOG_WARN | LOG_INFO | LOG_DBG | LOG  | LOG_HEX |

|---|---------|----------|----------|---------|------|---------|

|   | 517     | 262      | 340      | 53      | 1085 | 2       |

Logging is implemented as follows: The developer uses a logging macro to insert log messages into the source code. Furthermore, he has to define the logging level (e.g., LOG\_ERROR) and the logging mask (e.g., LM\_COM). The logging level is set by a macro – there exists one for every level. The logging mask is the first parameter of the macro followed by the message and the arguments that should be

```

/* logging macro */

ret = 12;

LOG_ERR(LM_ALL, "layer2_init returned %d %s\n", ret,

time_buffer);

/* logging macro resolved */

log_(LL_ERR, LM_ALL, "layer2_init returned %d %s\n",

ret, time_buffer);

/* log message */

<E>LM_ALL: layer2_init returned 12 2014-02-16_13

.52.14.012

```

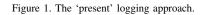

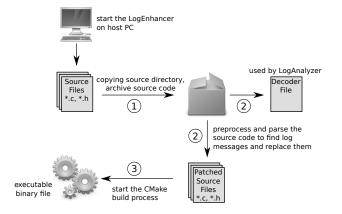

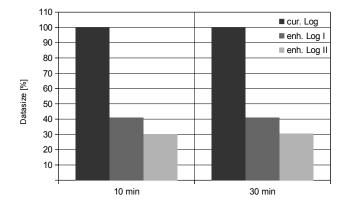

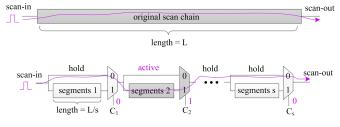

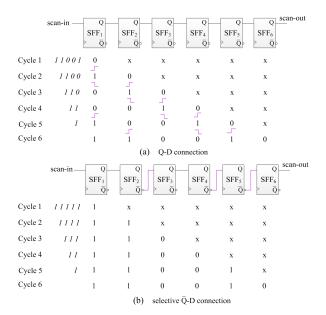

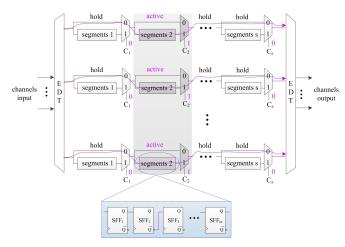

logged. The text string of the message is often put together using several ANSI/ISO C functions and finally output to *stdout*. In order to get a coherent logging style, the use of these macros is enforced by a strict development process using various approaches like code-reviews or static code analysis. Hence, our approach must comply with the same rules.