# **CENICS 2017**

The Tenth International Conference on Advances in Circuits, Electronics and Micro-electronics

ISBN: 978-1-61208-585-2

September 10 - 14, 2017

Rome, Italy

# **CENICS 2017 Editors**

Alie El-Din Mady, Senior Research Scientist, United Technologies Research Center (UTRC) – Cork, Ireland Timm Bostelmann, FH Wedel (University of Applied Sciences), Germany Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany

# **CENICS 2017**

# Forward

The Tenth International Conference on Advances in Circuits, Electronics and Microelectronics (CENICS 2017), held between September 10-14, 2017 in Rome, continued a series of events initiated in 2008, capturing the advances on special circuits, electronics, and microelectronics on both theory and practice, from fabrication to applications using these special circuits and systems. The topics covered fundamentals of design and implementation, techniques for deployment in various applications, and advances in signal processing.

Innovations in special circuits, electronics and micro-electronics are the key support for a large spectrum of applications. The conference was focusing on several complementary aspects and targets the advances in each on it: signal processing and electronics for high speed processing, micro- and nano-electronics, special electronics for implantable and wearable devices, sensor related electronics focusing on low energy consumption, and special applications domains of telemedicine and ehealth, bio-systems, navigation systems, automotive systems, home-oriented electronics, bio-systems, etc. These applications led to special design and implementation techniques, reconfigurable and self-reconfigurable devices, and require particular methodologies to be integrated on already existing Internet-based communications and applications. Special care is required for particular devices intended to work directly with human body (implantable, wearable, ehealth), or in a human-close environment (telemedicine, house-oriented, navigation, automotive). The mini-size required by such devices confronted the scientists with special signal processing requirements.

The conference had the following tracks:

- Design, models and languages

- Electronics technologies

- Reconfigurable Architectures, Tools and Applications

- Cyber-Physical Security

We take here the opportunity to warmly thank all the members of the CENICS 2017 technical program committee, as well as all the reviewers. The creation of such a high quality conference program would not have been possible without their involvement. We also kindly thank all the authors that dedicated much of their time and effort to contribute to CENICS 2017. We truly believe that, thanks to all these efforts, the final conference program consisted of top quality contributions.

We also gratefully thank the members of the CENICS 2017 organizing committee for their help in handling the logistics and for their work that made this professional meeting a success.

We hope that CENICS 2017 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in the field of circuits, electronics and microelectronics. We also hope that Rome, Italy provided a pleasant environment during the conference and everyone found some time to enjoy the historic charm of the city.

### **CENICS 2017 Chairs**

### **CENICS Steering Committee**

Falk Salewski, Muenster University of Applied Sciences, Germany Chun-Hsi Huang, University of Connecticut, USA Marc Sevaux, Université de Bretagne-Sud, France Vladimir Privman, Clarkson University - Potsdam, USA Diego Ettore Liberati, National Research Council of Italy, Italy Julio Sahuquillo, Universitat Politècnica de València, Spain Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Bartolomeo Montrucchio, Politecnico di Torino, Italy Petr Hanáček, Brno University of Technology, Czech Republic

### **CENICS Research/Industry Committee**

John Vardakas, Iquadrat Informatica, Barcelona, Spain Laurent Fesquet, TIMA laboratory | Grenoble Institute of Technology, France Christian Wögerer, PROFACTOR GmbH, Austria Miroslav Velev, Aries Design Automation, USA Ivo Stachiv, Institute of Physics | Czech Academy of Sciences, Prague, Czech Republic / Harbin Institute of Technology | Shenzhen Graduate School, Shenzhen, China Amir Shah Abdul Aziz, TM Research & Development, Malaysia

### CENICS 2017 Committee

### **CENICS Steering Committee**

Falk Salewski, Muenster University of Applied Sciences, Germany Chun-Hsi Huang, University of Connecticut, USA Marc Sevaux, Université de Bretagne-Sud, France Vladimir Privman, Clarkson University - Potsdam, USA Diego Ettore Liberati, National Research Council of Italy, Italy Julio Sahuquillo, Universitat Politècnica de València, Spain Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Bartolomeo Montrucchio, Politecnico di Torino, Italy Petr Hanáček, Brno University of Technology, Czech Republic

### **CENICS Research/Industry Committee**

John Vardakas, Iquadrat Informatica, Barcelona, Spain Laurent Fesquet, TIMA laboratory | Grenoble Institute of Technology, France Christian Wögerer, PROFACTOR GmbH, Austria Miroslav Velev, Aries Design Automation, USA Ivo Stachiv, Institute of Physics | Czech Academy of Sciences, Prague, Czech Republic / Harbin Institute of Technology | Shenzhen Graduate School, Shenzhen, China Amir Shah Abdul Aziz, TM Research & Development, Malaysia

### **CENICS 2017 Technical Program Committee**

Kelum Akurugoda Gamage, Lancaster University, UK Adel Al-Jumaily, University of Technology, Sydney, Australia Mohammad Amin Amiri, Malek Ashtar University of Technology, Islamic Republic of Iran Amir Shah Abdul Aziz, TM Research & Development, Malaysia Timm Bostelmann, FH Wedel (University of Applied Sciences), Germany Hamza Bouzeria, Constantine - 1- University, Algeria Khalid Bouziane, Université Internationale de Rabat, Morocco David Cordeau, XLIM UMR CNRS 7252, France Javier Diaz-Carmona, Technoligical Institute of Celaya, Mexico Alie El-Din Mady, United Technologies Research Center, Cork, Ireland Diego Ettore Liberati, National Research Council of Italy, Italy Laurent Fesquet, TIMA laboratory | Grenoble Institute of Technology, France Patrick Girard, LIRMM, France Petr Hanáček, Brno University of Technology, Czech Republic Houcine Hassan, Universitat Politècnica de València, Spain Chun-Hsi Huang, University of Connecticut, USA Jose Hugo Barron-Zambrano, Universidad Autonoma de Tamaulipas, Mexico Wen-Jyi Hwang, National Taiwan Normal University, Taiwan Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Eric Kerherve, IMS Laboratory, France Junghee Lee, University of Texas at San Antonio, USA Kevin Lee, Nottingham Trent University, UK Yo-Sheng Lin, National Chi Nan University, Taiwan Ravi M Yadahalli, SG Balekundri Institute of Technology, India Brian M. Sadler, Army Research Laboratory, Adelphi, USA Carlos M. Travieso-González, Universidad de Las Palmas de Gran Canaria, Spain Ravi M. Yadahalli, S G Balekundri Institute of Technology, Belagavi, Karnataka, India Cristina Meinhardt, Federal University of Rio Grande (FURG), Brazil Harris Michail, Cyprus University of Technology (CUT), Cyprus Amalia Miliou, Aristotle University of Thessaloniki, Greece Bartolomeo Montrucchio, Politecnico di Torino, Italy Ioannis Moscholios, University of Peloponnese, Greece Shinobu Nagayama, Hiroshima City University, Japan Djemai Naimi, Université Mohamed Khider - Biskra, Algeria Arnaldo Oliveira, UA-DETI/IT-Aveiro, Portugal Nikos Petrellis, TEI of Thessaly, Greece Vladimir Privman, Clarkson University - Potsdam, USA Càndid Reig, University of Valencia, Spain Piotr Remlein, Poznan University of Technology, Poland Djohra Saheb, Centre de Développement des Energies Renouvelables (CDER), Algeria Julio Sahuquillo, Universitat Politècnica de València, Spain Falk Salewski, Muenster University of Applied Sciences, Germany Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany Sandra Sendra, Universidad de Granada, Spain Marc Sevaux, Université de Bretagne-Sud, France Saeideh Shirinzadeh, University of Bremen, Germany Ivo Stachiv, Institute of Physics | Czech Academy of Sciences, Prague, Czech Republic / Harbin Institute of Technology | Shenzhen Graduate School, Shenzhen, China Francisco Torrens, Universitat de Valencia, Spain John Vardakas, Iquadrat Informatica, Barcelona, Spain Miroslav Velev, Aries Design Automation, USA Manuela Vieira, ISEL-CTS-UNINOVA, Portugal Jin Wei, University of Akron, USA Robert Wille, Institute for Integrated Circuits | Johannes Kepler University, Linz, Austria Christian Wögerer, PROFACTOR GmbH, Austria Piotr Zwierzykowski, Poznan University of Technology, Poland

### **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

### **Table of Contents**

| Evaluating Heterogeneous Architectures based on Zynq AP SOC for Real-Time Video Processing Fanny Spagnolo, Stefania Perri, and Pasquale Corsonello                                                                        | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

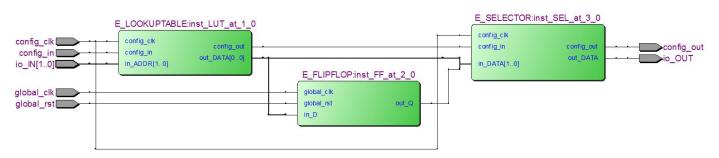

| Table Reference-Based Acceleration of a Lithography Hotspot Detection Method Based on Approximate String Search Shuma Tamagawa, Masato Inagi, Shinobu Nagayama, and Shin'ichi Wakabayashi                                 | 8  |

| Energy-Efficient Real-Time Operating Systems: An Approach using Dynamic Frequency Scaling and Worst-Case Execution Time Aware Scheduling <i>Thomas Jerabek, Benjamin Aigner, Florian Gerstmayer, and Jurgen Hausladen</i> | 15 |

| Low Power Charge Recycling D-FF<br>Karol Niewiadomski and Dietmar Tutsch                                                                                                                                                  | 21 |

| A Watt-Level 4G LTE CMOS Reconfigurable Power Amplifier with Efficiency Enhancement in Power Back-Off <i>Giap Luong, Jean-Marie Pham, Pierre Medrel, and Eric Kerherve</i>                                                | 28 |

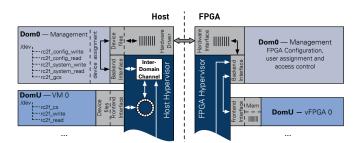

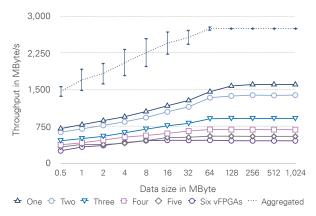

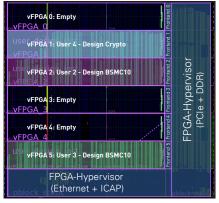

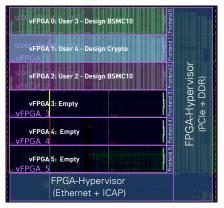

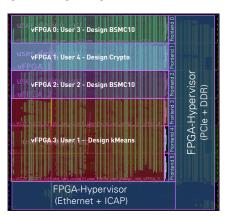

| Virtualizing Reconfigurable Hardware to Provide Scalability in Cloud Architectures<br>Oliver Knodel, Paul R. Genssler, and Rainer G. Spallek                                                                              | 33 |

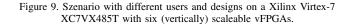

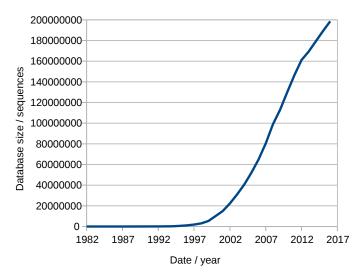

| Local Alignment Search in Genetic Sequences on a Low-Cost FPGA<br>Timm Bostelmann, Thomas Fabian Starke, and Sergei Sawitzki                                                                                              | 39 |

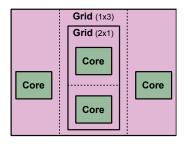

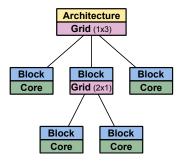

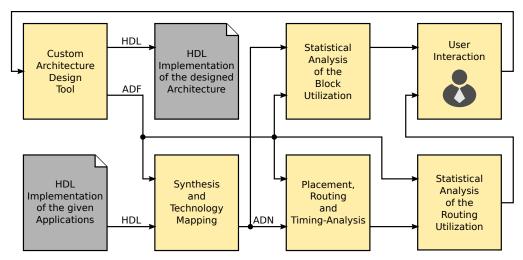

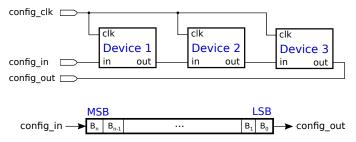

| A Synthesizable VHDL Export for the Custom Architecture Design Tool CustArD<br>Thomas Fabian Starke, Timm Bostelmann, Helga Karafiat, and Sergei Sawitzki                                                                 | 44 |

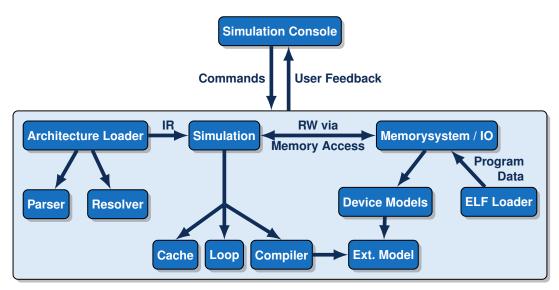

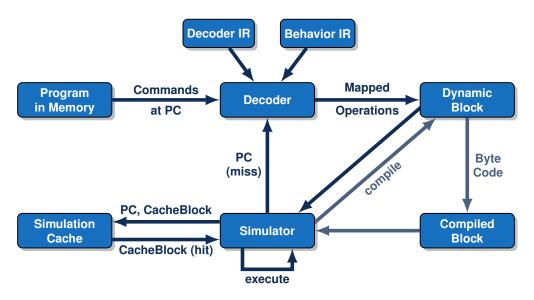

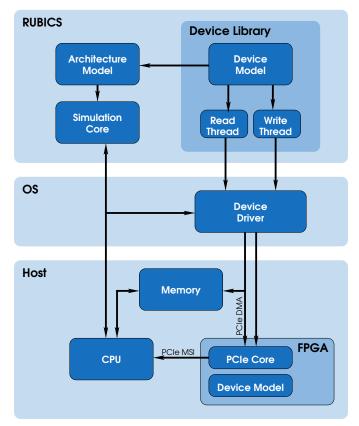

| Custom Hardware Integration into DBT-based Processor Simulation<br>Steffen Kohler and Rainer Spallek                                                                                                                      | 49 |

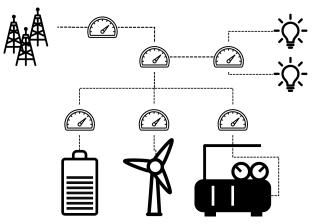

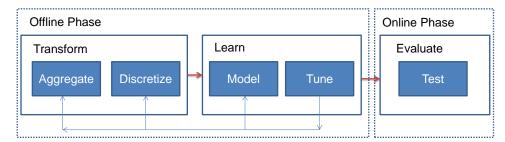

| Towards an Implementation of Data Analytics for Smart Grid Security<br>Jacobo Blanco, Silvio La Porta, Niamh O Mahony, Rohan Chabukswar, Alie El-Din Mady, and Menouer<br>Boubekeur                                       | 55 |

| Towards Secure Building Management System based on Internet of Things<br>Alie El-din Mady, Ruben Trapero, Antonio Skarmeta, and Stefano Bianchi                                                                           | 61 |

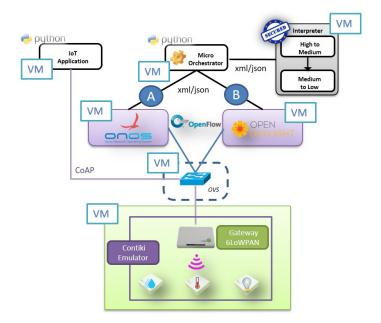

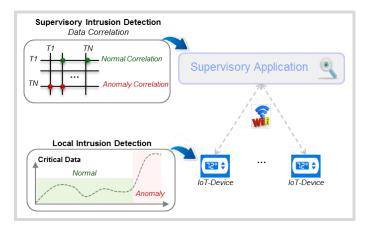

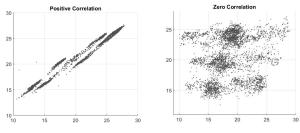

| Anomaly-Based Intrusion Detection System for Embedded Devices on Internet<br>Deepak Mehta, Alie El-Din Mady, Menouer Boubekeur, and Devu Manikantan Shila                                                                 | 65 |

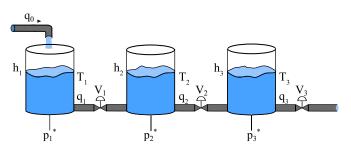

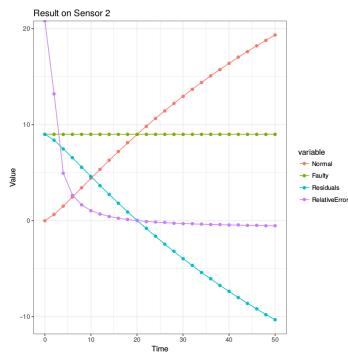

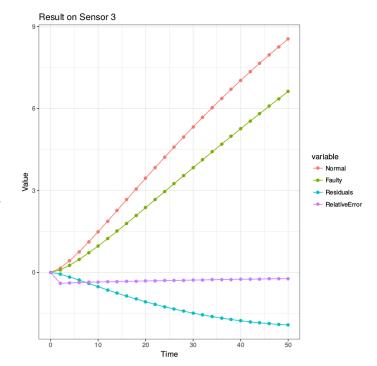

| Physics-Based Methods for Distinguishing Attacks from Faults<br>Gregory Provan and Riccardo Orizio                                                                                                                        | 70 |

## Evaluating Heterogeneous Architectures based on Zynq AP SOC for Real-Time Video Processing

Fanny Spagnolo, Stefania Perri, Pasquale Corsonello Department of Electronics, Computer Sciences and Systems DIMES - University of Calabria Arcavacata di Rende, Italy e-mail: f.spagnolo@dimes.unical.it, perri@dimes.unical.it, p.corsonello@unical.it

Abstract-Embedded systems are known as valid candidates to efficiently support image and video processing algorithms. Their high flexibility, speed performances and low power consumption are mainly due to the joint design of their software and specific hardware portions. The Zynq All Programmable System on Chip, that integrates ARM processor and high performance programmable logic resources, is nowadays often preferred to the more traditional realization platforms, such as Application Specific Integrated Circuits (ASICs) and Digital Signal Processors (DSPs). In this paper, we evaluate two different design strategies, each with its own Zynq-based support platform, giving to the designers useful hints on how to identify the best design choices for the target application. The first support platform presented here also makes use of an embedded operating system (OS); it significantly limits the required design efforts and time-tomarket. The second architecture is realized without the OS support, and of course reaches much higher performances than the former, but requiring higher development and verification times. Both platforms exploit a hardware accelerator for the function of interest. As a case study, a simple but complete image processing architecture has been designed by using both the above platforms. Performances measurements revealed that an approximate speed improvement between 4 and 52 times could be obtained with respect to an all-software implementation.

Keywords-Embedded Systems; Image Processing; Zynq.

### I. INTRODUCTION

In the last few years, the development of even more complex and computationally intensive video processing algorithms has been made possible due to the everincreasing technology progress. Many of these algorithms are adopted in a large variety of applications where realtime performances play an important role. In these cases, software-oriented implementations, running on general purpose CPUs, might not satisfy the tight speed constraints. Faster and more efficient implementations can be achieved with the aid of hardware accelerators that allow exploiting proper computational parallelisms. Embedded systems are a well known approach to speed up image and video processing algorithms by conjunct software/hardware special designs [1]. Such heterogeneous architectures allow trading off the advantages offered by the flexible software and the high performance hardware portions of the design [2]. Nowadays, among several possible realization platforms, the FPGA-based is the most interesting one. Its reduced design efforts and time-to-market make such an approach more appreciated than those based on ASICs fabrication [3]. The lower power dissipation and higher speed performances attainable by using such realization strategy make it preferable with respect to the DSP-based counterparts [4].

Usually, designing an embedded system for video processing, the designer must take into account that most algorithms perform both pixel-level and frame-level computations. Due to their higher computational complexity, pixel-level processing have a great benefit by the inclusion in the embedded system of a dedicated hardware accelerator. On the contrary, frame-level elaborations often process only few frame descriptors. Thus, they do not represent a bottleneck for the overall application. In this case, a pure software implementation can be easier, more flexible and does not compromise the system performances. It is then clear why, in order to conjugate the high-speed capability of a hardware implementation with the flexibility provided by a software design, heterogeneous System-on-Chips (SoCs) based on FPGA have been recently recognized as the most promising approach [5].

However, hardware-software (HW/SW) co-design shows several challenges for the designer. Not only the application has to be partitioned into software and hardware tasks, but also the communication between them has to be efficiently managed.

In this paper, we evaluate two different design strategies for the design and the implementation of real-time embedded systems for image and video processing based on a FPGA SoC. Each of the two designs presented here has its own strengths and weaknesses. The former shows an extreme flexibility and a moderate performance, whereas the latter requires more design efforts but allows much higher speed performance to be reached. As a case study, a complete image processing architecture, which includes image capturing from a webcam, Sobel filtering and output visualization on a monitor, has been implemented. All experiments have been performed by using a Zedboard equipped with the Xilinx Zynq XC7Z020-CLG484 SoC. Performance measurements revealed that the frame rates of such designed embedded systems range between 4 and 52 times the frame rate attainable by a pure software counterpart. The rest of the paper is organized as follows. In Section II, a brief background and the most relevant state of the art related works are reviewed. The first evaluated architecture is introduced in Section III, whereas Section IV describes an example of application to perform fair comparisons. A different design approach is then investigated in Section V. Finally, some conclusions are drawn in Section VI.

### II. BACKGROUND AND RELATED WORKS

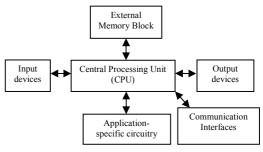

The essence of embedded systems design is implementing a specific set of functions in order to accomplish constraints on performance, costs, emissions, power consumption, etc [6]. Figure 1 shows the typical architecture of a generic embedded system. In general, one or more programmable processing units (CPUs) are used. Depending on the application domain, the embedded systems can have external memory blocks, communication interfaces and several I/O peripherals. While CPUs are traditionally software programmed, custom application specific circuits accelerate more time consuming processes. The first preliminary design step is the efficient HW/SW partitioning of the target application. It consists of splitting the application into computational tasks to be executed either by software routines or by hardware modules. Depending on this partitioning, speed performances and design complexity can be traded off. The generally used approach is to profile the application by means of specific CAD tools [7] in order to indentify its computational loads. Speed performances can be optimized allocating the processing of the most time-consuming tasks to custom hardware accelerators. The remaining non-critical tasks are executed by software routines running on the host general purpose processor. To avoid communication bottlenecks, in a similar approach, the host processor and the hardware accelerators must exchange and transfer data to each other with high throughput and low latency.

The emerging approach based on heterogeneous programmable SoCs is stimulating many application fields [8]. In this section, a group of significant related works are briefly reviewed.

A prototyping environment for heterogeneous CPU/FPGA systems is described in [9], in which a host machine is coupled to a Xilinx Virtex 6 FPGA through the PCI Express Bus. As shown in [10], the limited bandwidth of the communication bus reduces the achievable performances.

A Cadence virtual platform modeling the Xilinx Zynq-7000 SoC is adopted in [11] to implement an Adaptive Cruise Control Unit. This virtual prototyping environment allows using the SystemC language for the portable implementation of software and hardware modules, thus

Figure 1. The typical structure of an Embedded System.

avoiding VHDL designs and speeding up the simulation of the overall system. A similar approach is adopted also in [12], where a very high abstraction design approach, based on the use of OpenCV and SystemC, is proposed as an efficient strategy to design embedded systems.

A study about the portability of the OpenCL programming model is, instead, presented in [13]. OpenCL is a framework for targeting heterogeneous platforms based on the C/C++ language.

This approach allows a HW/SW co-design that is independent of the adopted hardware platform to be obtained. Thus, the code can be easily re-targeted to different platforms. In [13], experiments conducted by using the Altera SDK for OpenCL (AOCL), however, demonstrate that the same test code performs differently on different platforms, thus requiring specific optimizations.

In [14], several real-time image processing algorithms are implemented on a Zynq-based hardware platform. This study exploits a task partitioning of the target application based on performances improvements. Linux operating system is hosted on the ARM CPU inside the Zynq to easily manage the video acquisition by software routines. An efficient communication strategy between hardware accelerators and the host CPU is realized through the AMBA Advanced Extensible Interface (AXI).

With the main objective of reducing the time-to-market of the developed system, the approach described in [15] exploits the Xillybus IP core to guarantee a fast communication between hardware and software components of the overall system. To this aim, the communication is managed by software thanks to some useful functions included in the Xillybus library.

In the next section, we evaluate such an approach as a generally valid support to design heterogeneous embedded system architectures for real-time image processing. The Xillinux open source operating system is hosted on the CPU and it manages the communication with the hardware implemented into the FPGA portion of the Zynq chip as a regular peripheral.

### III. THE XILLYBUS-BASED PLATFORM

The main target of the platform described below is to furnish an efficient hardware support to develop real-time

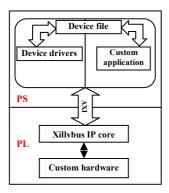

Figure 2. Xillybus-based platform. The PS section hosts the OS components, whereas the PL section implements hardware accelerators and Xillybus IP core.

image and video processing applications in embedded systems, with reduced implementation time.

The platform evaluated in this section is structured as depicted in Figure 2. The Zynq processing system (PS) consists of a dual core ARM Cortex – A9 processor, while the programmable logic (PL) is based on the Artix-7 FPGA fabric for minimizing power consumption.

The ARM processor is able to host OSs such as Linux, Real Time Operating System (RTOS), Windows, etc. The Zedboard is also equipped with 512 MB DDR3 memory and a 256Mb 4-bit SPI Serial NOR Flash memory. The latter supports speeds up to 400Mbps and hence it is suitable for storing boot loaders and kernel of one of the above OSs.

The system detailed below exploits a set of precompiled sub-systems, namely the Xillybus package, able to facilitate the communication tasks between the PS, the external peripherals and the accelerators. The Xillybus package makes also available the Xillinux open source OS that is a complete graphical Ubuntu 12.04 LTS-based Linux distribution, well suitable for rapid development of mixed software/logic designs [16]. It is a collection of software tools that supports roughly the same capabilities of a personal desktop computer running Linux. Xillybus distribution comes with two different synthesizable cores: the XillyLite IP core that allows a simple direct address/data transfer; and the Xillybus IP core that allows data streams to be transferred to/from the custom hardware accelerator [17].

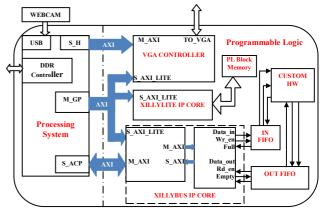

The designed architecture is illustrated in Figure 3. It can be observed that a XillyLite core is used to access a block RAM, whereas the Xillybus core is adopted to transfer data from the PS to/from the custom hardware accelerator [18]. All IP cores are also connected to the PS by an AXI-Lite interface.

When connected to the Xillybus IP core, the hardware accelerators can be accessed by the PS like a common peripheral, which communicates with the OS through specific device drivers.

The interface between the software drivers and the software application is represented by the device files provided by Xillybus. These files can be opened, read and written like any files inside the user space application, so it is possible to implement a high level abstraction for PS-PL communication.

The PS manages the data transfer to capture the frames from a webcam through the USB port and to store them into the DDR3 external memory. Other memory accesses, related to the data transfers to/from the custom hardware accelerator, are governed by the Xillybus IP core through the high performances ports in the PS section. The acquisition operation is easily implemented in software by using video libraries and camera drivers. Whereas, the PL was used to hardware implement the following components:

- The Xillybus IP core that communicates with the PS through the AXI full and AXI Lite interfaces;

- The XillyLite IP core that communicates with the PS through the AXI Lite interface;

- The custom hardware accelerator;

- Two FIFOs, used as input and output interfaces between the Xillybus core and the custom hardware accelerator;

- A VGA controller connected to an external monitor that displays the output of the custom hardware accelerator stored in the DDR3 external memory.

In the designed architecture, the processor works as master during the configuration of the VGA controller, the XillyLite IP core and the Xillybus IP core. This configuration corresponds to a control signals transfer, needed to inform the hardware IP cores about the image resolution, the DDR memory addresses etc.

Each data transfer through an AXI interface occurs as summarized in the following:

- In a read process, the slave device address is sent by the master interface over the read address channel. Then, the addressed slave interface sends the corresponding data over the read data channel to the master.

- In a write process, the master interface sends the slave device address to which the data is to be written and corresponding data. On successful write at the slave interface, the slave sends a response over the write response channel to flag the transfer completion.

Figure 3. Architecture used within the ZedBoard to evaluate the Xillybusbased platform.

An AXI Interconnect IP core multiplexes the access by the master to the three slaves and the Xillybus IP core acts as an interface between the PS and the custom hardware accelerator. This architecture can be easily customized to perform virtually any image and video processing algorithm without re-design either the top-level architecture or the interface modules required to acquire input images/videos and to display/store the resulting frames.

Data transferred to/from the PS from/to the hardware accelerator flows through the input and output FIFOs, as shown in Figure 3. FIFOs can be configured according to the applications requirements, but they must comply with the constraints of the device drivers provided by Xillybus. As an example, the Xillybus drivers can be configured to transfer 8, 16 or 32-bit data words so the data width of the FIFOs must be set accordingly. The *wr\_en*, *rd\_en*, *full* and *empty* control signals manage the synchronization between the Xillybus IP core and the hardware accelerator.

The complete data flow implemented within an embedded system designed by using our platform is described in the following:

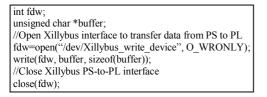

- The PS converts the RGB frame, captured by the webcam, into the 8-bit grayscale format and, subsequently, it transfers the pixels to the external DDR3 block memory. The frame is transferred from the DDR3 memory to the PL through the Xillybus interface. This operation is performed by the software routine running on the PS, which communicates with the Xillybus drivers through the available "open" and "write" functions applied on the specific device file, as shown in Figure 4. Then, the pixel transfer from PS to the Xillybus IP core occurs through the high performance S\_AXI\_ACP port. As a response, the Xillybus IP core activates the write enable (*wr\_en*) signal of the input FIFO.

- If the input FIFO is not empty and the hardware accelerator is ready to receive the input pixels, the read enable (*rd\_en*) signal is asserted and a stream of pixels is sent to the hardware accelerator.

- When valid data is available on the output port of the hardware accelerator, the latter asserts the write enable (*wr\_en*) signal of the output FIFO, which receives a stream of data produced by the user-defined computational logic. The output data stream continues until the output FIFO becomes full. If this condition occurs, the output FIFO asserts its *full* signal and the hardware accelerator temporarily stalls the transfer.

Figure 4. Use of "open" and "write" functions in the software routine.

| int fdr;<br>unsigned char *buffer;<br>//Open Xillybus interface to transfer data from PL to PS<br>fdr=open("/dev/Xillybus_read_device", O_RDONLY);<br>read(fdr, buffer, sizeof(buffer));<br>//Close Xillybus PL dto_PS interface |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| //Close Xillybus PL-to-PS interface                                                                                                                                                                                              |

| close(fdr);                                                                                                                                                                                                                      |

Figure 5. Use of "open" and "read" functions in the software routine.

- The software running on the PS invokes the "open" and "read" functions of the Xillybus driver, as described in Figure 5, so data stored in the output FIFO is transferred to the DDR3 through the S\_AXI\_ACP/Xillybus connection. In hardware, this operation corresponds to assert the *rd en* signal of the output FIFO.

- The output image is finally transferred from the DDR3 to the VGA controller that is connected to an external monitor. The PS is involved in this operation only to send the control signals to the VGA controller through its M\_AXI GP port. Pixels to display are transferred from the DDR3 to the VGA controller through the high performance S\_AXI\_HP port of the PS. The latter is not involved during the data transfer so it can run the next software routine.

In the proposed design support platform, the Xillybus IP core and the custom hardware accelerator work with the same clock, so the write/read operations to/from the input and output FIFOs occur at the same rate. The clock is produced by the PS with a frequency of 100MHz, which is the highest frequency supported by the Xillybus IP core [19]. The usage of synchronous streams is the preferred choice when tight synchronization is needed between the software running on the PS and the hardware implemented in the PL. However, in order to increase performances, multiple clock domains can be adopted if the hardware accelerator can run at clock frequencies higher than 100MHz. In such a case, asynchronous FIFOs with different input and output clock frequencies have to be employed. In particular, the write (read) operation into (from) the input (output) FIFO is performed at the Xillybus clock rate, whereas the write (read) operation into (from) the output (input) FIFO is performed at the clock rate of the hardware accelerator.

### IV. THE CASE STUDY: A SOBEL FILTER IMPLEMENTATION

As an example of application, the above described design platform has been used to implement an embedded system which filters digital images. The  $3\times3$  Sobel filter [20] is hardware implemented and applied to  $320\times240$  pixels frames captured by the external camera. Image filtering has been chosen as the case study since it has a computational complexity sufficiently high to highlight the advantages offered by the HW/SW co-design over the allsoftware counterpart.

The hardware accelerator has been developed with the Vivado High Level Synthesis (HLS) tool that allows describing the hardware circuit in a high level programming

| Sob  | el accel | erator       | Cu   | istom F | IFOs         | Xil  | lybus II | core         | VGA  | Contro<br>core | oller IP     | Xill  | yLite II | ° core       |

|------|----------|--------------|------|---------|--------------|------|----------|--------------|------|----------------|--------------|-------|----------|--------------|

| LUTs | FFs      | 32K<br>BRAMs | LUTs | FFs     | 32K<br>BRAMs | LUTs | FFs      | 32K<br>BRAMs | LUTs | FFs            | 32K<br>BRAMs | LUTs  | FFs      | 32K<br>BRAMs |

| 212  | 172      | 1            | 90   | 96      | 1            | 3011 | 2690     | 1            | 499  | 779            | 1            | 67    | 94       | 0            |

| 0.4% | 0.1%     | 0.7%         | 0.1% | 0.1%    | 0.7%         | 5.6% | 2.5%     | 0.7%         | 0.9% | 0.7%           | 0.7%         | 0.12% | 0.1%     | (0%)         |

TABLE I. RESOURCE UTILIZATION.

language (C++) and converting the code into a synthesizable RTL description. Input and output interfaces of the custom hardware accelerator have been configured as FIFOs, in order to guarantee the compatibility with the two FIFOs connected to the Xillybus IP core. The FIFOs have a data width and a depth of 8 bit and 2048 words, respectively.

Table I summarizes the overall FPGA resources utilization of the implemented architecture. The number of the total used look-up tables (LUTs) is very limited, about 7% of the LUTs available in the XC7Z020-CLG484 chip; the number of required flip-slops (FFs) and 32Kbyte block RAMs (32K BRAMs) is even lower (3.5% and 2.8%, respectively).

The software application, running on the PS, exploits OpenCV library functions [21] to manage the input frames captured by the USB camera. The input pixels are converted from the RGB to the 8-bit grayscale format and transferred to the DDR3 memory. The software application is responsible for transferring the pixels to the Xillybus IP core, retrieving the output pixels from the hardware accelerator and storing them to the DDR3 memory. Finally, the software application starts the data transfer from the DDR3 to the VGA controller. Figure 6 shows two output video frames obtained by the implemented architecture.

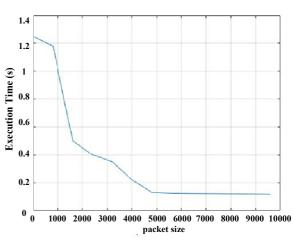

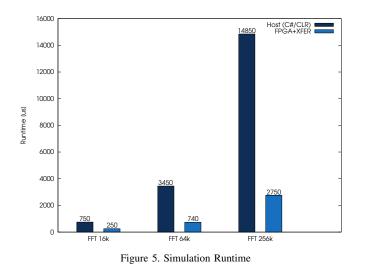

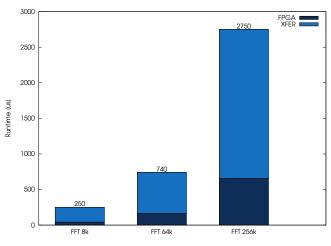

To measure execution time of each task, the appropriate software timing library has been used. Since the data transfer through the Xillybus can be performed by varying the number of bytes transferred at each write/read function call, we evaluated the execution time as a function of the bytes packet size. As depicted in Figure 7, the total execution time drastically decreases when the packet size increases. But, the minimum execution time of about 118.3 ms is reached for a packet size of  $\approx$ 5000 bytes and it is maintained until 9600 bytes.

Figure 6. Some input and output video frames.

Figure 7. Execution time vs. the packet dimension.

TABLE II. EXECUTION TIMES.

| Hardware<br>Sobel filter | Software<br>application | Communication | All-software<br>Sobel filter |

|--------------------------|-------------------------|---------------|------------------------------|

| 2.3 ms                   | 100 ms                  | 16 ms         | 490 ms                       |

This result suggests to adopt transfer of  $\approx$ 5000 bytes each, because this also limits the depth of the input and output FIFOs.

Table 2 shows the timing breakdown that is split into three main contributions: the hardware processing time (Sobel filtering), the PL-PS communication time ("write, "read" and "open" of the Xillybus driver) and the remaining software execution time (RGB to grayscale conversion and data streaming from/to the DDR3 managed by the PS) per frame.

As expected, the software execution time represents the highest contribution, mainly due to the OpenCV functions for the management of input frame, the format conversion and the output frame visualization. The hardware processing and the communication between PS and Xillybus IP core account only for the 15.5% of the overall execution time.

In order to estimate the speed-up obtained by the custom hardware accelerator, a pure software routine performing the same Sobel filtering has been characterized. The latter has been executed by the ARM processor hosted in the PS, which operates at a 666.66 MHz running frequency. Measurements reported in Table 2 show the benefits obtained by the heterogeneous design approach. A gain of about 4x has been achieved.

Even though a direct comparison between our results and those reported in [15] cannot be performed, due to the different user application, a brief discussion is appropriate. In [15], a Xillybus-based platform performing the Harris Corner Detection function on 512x384 images has been implemented and evaluated. When the PL is clocked at 100 MHz and the 32-bit Xillybus software interface is adopted, the total communication and hardware processing time is about 15 ms. The latter is approximately 3.3ms lower than result reported in Table 2, which instead has been obtained adopting the 8-bit Xillybus software interface. If the 32-bit Xillybus software interface is used in the architecture of Figure,3, the communication time is reduced correspondingly.

### V. THE VDMA-BASED ALTERNATIVE

The high level design approach used above employs a ready-to-use communication solution between hardware and software components. Due to this, it significantly reduces design efforts, the development time and the hardware design expertise required for realizing a complete embedded system for video processing applications. Of course, such a design strategy negatively impacts the overall speed performances. In particular, some considerations can be done in reference to the Xillybus bandwidth.

The FIFO configuration provided by Xillybus has a maximum bandwidth of about 200 MB/s for each transfer direction [17]. On the contrary, the Zynq PS high performance ports are able to access the DDR3 memory achieving a bandwidth of 1600 MB/s for a 64-bit transfer at 100 MHz clock rate [22].

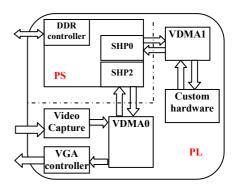

In this section, we examine an alternative design, based on the direct use of Video Direct Memory Access (VDMA) IP cores [23]. Using this approach, much more architectures design knowledge and digital system debugging practice are required. The VDMA is a soft core, which provides high bandwidth access to external memory and video processing IP cores with AXI-Stream interface. The architecture designed in accordance with this strategy is illustrated in Figure 8. In this case the PS does not support an OS, thus the system is oriented to bare-metal application architectures. An OmniVision OV7670 CMOS Camera has been connected through an I2C interface and an appropriate frame capture control sub-system is required. The VDMA0 transfers captured frames to the DDR3 and, then, after the elaboration, from the DDR3 to the VGA display port. The VDMA1 transfers the video stream to the custom hardware accelerator that performs the specific video algorithm. After that, the VDMA1 writes back the filtered results into the DDR3 memory.

Using High Performance AXI ports to access the external memory allows the computational load of the processor to be significantly reduced. Furthermore, by using two different High Performance ports, parallel operations to/from the DDR3 can be performed, thus obtaining a further considerable performance improvement. In fact, a new captured frame can be stored, or a result frame can be displayed, while the VDMA1 transfers the pixel stream to/from the hardware accelerator.

Figure 8. Architecture used within the ZedBoard to evaluate the VDMA-based platform.

Due to the overlap between the two phases above mentioned, this architecture reaches a processing rate much higher than the structure exploiting the Xillybus IP Cores. When the same Sobel filter accelerator is implemented within this structure, a total execution time of only  $\approx$ 9.2 ms is achieved, thus leading to an overall performance ~13 times higher. This result has been obtained with a clock rate of 100MHz for the PL section, while the Video Capture IP core operates at 30 frames per second in VGA resolution.

#### VI. CONCLUSIONS

In the development of an embedded system based on heterogeneous SoCs, of course, the first important design step is the efficient HW/SW partitioning of the target application. After that, on the basis of the design environment, several other significant choices have to be done. When only high level description is desired, several precompiled supports could be of great help. As shown in this paper, an almost complete solution is offered by the Xillybus package that contains appropriate communication sub-modules and a light OS.

We designed a test architecture to evaluate the speed improvement attainable with such supports and measured a speed up of  $\approx$ 4 times with respect to a pure software typical image processing elaboration. Such an approach allows very easy interface between the designed architecture and peripherals.

On the contrary, when the speed performance is the main concern, a direct and on-purpose design of the entire architecture is preferable. In such a case, a further x13 speed up has been observed, but at the expense of much more design effort and verification time.

#### ACKNOWLEDGMENT

Authors wish to thank Dr. Fabio Frustaci and Dr. Giovanni Staino for the helpful discussions during the present work.

#### REFERENCES

W. Wolf, "The Future of Multiprocessor Systems-on-Chips" Proceedings of the 41st annual Design Automation Conference (DAC '04), pp. 681-685, June 7-11 2004.

- [2] B. Roux, M. Gautier, O. Sentieys, and S. Derrien, "Communication-Based Power Modelling for Heterogeneous Multiprocessor Architecture", IEEE 10th International Symposium on Embedded Multicore /Many-core Systems-on-Chip (MCSoC 2016), pp. 209-216, Sep 2016.

- [3] J.A. Kalomiros and J. Lygouras, "Design and evaluation of a hardware/software FPGA-based system for fast image processing", Microprocessors and Microsystems, vol. 32, issue 2, March 2008.

- [4] R. J. Petersen and B. L. Hutchings, "An assessment of the suitability of FPGA-based systems for use in digital signal processing". In: Moore W., Luk W. (eds) Field-Programmable Logic and Applications. FPL 1995. Lecture Notes in Computer Science, vol. 975, pp. 293-302. Springer, Berlin, Heidelberg

- [5] J. Teich, "Hardware/Software Codesign: The Past, the Present, and Predicting the Future", Proceedings of the IEEE, vol. 100, Issue: Special Centennial Issue, pp. 1411-1430, May 13 2012.

- [6] A. Sangiovanni-Vicentelli and G. Martin, "Platform –based Design and Software Design Methodology for Embedded Systems", IEEE Design & Test of Computers, IEEE press, vol. 18, issue 6, pp. 23-33, Nov/Dec 2001, doi: 10.1109/54.970421.

- [7] R. Ernst, "Codesign of Embedded Systems: status and trends", IEEE Design & Test of Computers, vol. 15, issue 2, pp. 45-54, Apr-Jun 1998, doi: 10.1109/54.679207.

- [8] D. Andrews, D. Niehaus, and P. Ashenden, "Programming models for hybrid CPU/FPGA chips", Computer, IEEE press, vol. 37, issue 1, pp. 118-120, Jan. 2004, doi: 10.1109/MC.2004.1260732.

- [9] G. Afonso, R.B. Atitallah, A. Loyer, J. Dekeyser, N. Belanger, and M. Rubio, "A prototyping environment for high performance reconfigurable computing" 6<sup>th</sup> International Workshop on Reconfigurable Communication-centric Systems-on-Chip (ReCoSoC), IEEE press, pp. 1-8, August 2011, doi: 10.1109/ReCoSoC.2011.5981497.

- [10] Y. Li, X. Zhao, and T. Cheng, "Heterogeneous Computing Platofrom Based On CPU+FPGA and Working Modes", 12<sup>th</sup> International Conference on Computational Intelligence and Security (CIS), IEEE press pp. 670-672, December 2016, doi: 10.1109/CIS.2016.0161.

- [11] P. Wehner, M. Ferger, D. Göhringer, and M. Hübner, "Rapid Prototyping of a Portable HW/SW Co-Design on he Virtual Zynq Platform using SystemC", IEEE 26<sup>th</sup> International SOC Conference (SOCC), IEEE press pp. 296-300, September 2013, doi: 10.1109/SOCC.2013.6749704.

- [12] J. Anders, M. Mefenza, C. Bobda, F. Yonga, Z. Aklah, and K. Gunn, "A hardware/software prototyping system for driving assistance investigations" in Journal of Real-Time Image Processing, vol. 11, issue 3, pp. 559-569, March 2016.

- [13] S.O. Ayat, M. Khalil-Hani, and R. Bakhteri, "OpenCL-based Hardware-Software Co-design Methodology for Image Processing Implementation on Heterogeneous FPGA Platform", 2015 IEEE International Conference on Control System, Computing and Engineering (ICCSCE), IEEE press pp. 36-41, November 2015, doi: 10.1109/ICCSCE.2015.7482154.

- [14] M.A. Altuncu, T. Guven, Y. Becerikli, and S. Sahin, "Real-Time System Implementation for Image Processing with Hardware/Software Co-design on the Xilinx Zynq Platform", International Journal of Information and Electronics

Engineering, vol. 5, no. 6, pp. 473-477, November 2015, doi: 10.7763/IJIEE.2015.V5.582.

- [15] I. Stratakos, D. Reisis, G. Lentaris, K. Maragos, and D. Soudris, "A Co-Design Approach For Rapid Prototyping Of Image Processing on SoC FPGAs"Proceedings of the 20th Pan-Hellenic Conference on Informatics (PCI '16), November 2016, ISBN: 978-1-4503-4789-1, doi: 10.1145/3003733.3003797.

- [16] Getting started with Xillinux for Zynq-7000 EPP v. 1.3 [Online]. Available from: http://xillybus.com/downloads/doc/xillybus\_getting\_started\_z ynq.pdf

- [17] B.M. Kambalur, K. Kumar, and K.S. Athrey, "A Study of Implementing Custom Application on Zynq AP SoC using Xillybus IP Core", ITSI Transactions on Electrical and Electronics Engineering (ITSI-TEEE), vol.. 2 pp. 35-37, issue 5-6, 2014.

- [18] Getting started with the FPGA Demo Bundle for Xilinx v. 2.6 [Online]. Available from: http://xillybus.com/downloads/doc/xillybus\_getting\_started\_x ilinx.pdf

- [19] Xillybus FPGA Designer's Guide v. 2.0 [Online]. Available from:

http://xillybus.com/downloads/doc/xillybus\_fpga\_api.pdf

- [20] N. Kanopoulos, N. Vasanthavada, R., and L. Baker, "Design of an Image Edge Detection Filter Using the Sobel Operator", IEEE Journal of Solid-State Circuits, vol. 23, issue 2, pp. 358-367, Apr 1988, doi: 10.1109/4.996.

- [21] About OpenCV [Online]. Available from: http://opencv.org/about.html

- [22] Zynq-7000 All Programmable SoC Technical Reference Manual, UG585 (v. 1.11) September 27, 2016 [Online]. Available from: https://www.xilinx.com/support/documentation/user\_guides/u g585-Zynq-7000-TRM.pdf

- [23] C. Kohn, "Partial Reconfiguration of a Hardware Accelerator on Zynq-7000 All Programmable SoC Devices" XAPP1159 Xilinx Jan. 21, 2013.

### **Table Reference-Based Acceleration of**

### a Lithography Hotspot Detection Method Based on Approximate String Search

Shuma Tamagawa, Masato Inagi, Shinobu Nagayama, Shin'ichi Wakabayashi email: shuma@lcs.info.hiroshima-cu.ac.jp, {inagi, s\_naga, wakaba}@hiroshima-cu.ac.jp Graduate School of Information Sciences, Hiroshima City University 3-4-1 Ozuka-higashi, Asaminami-ku, Hiroshima, 731-3194 Japan

*Abstract*—In nanoscale large-scale integration (LSI) manufacturing, there exist hotspots on mask patterns, which cause failures of pattern transfer. Such hotspots are detected by optical simulation to remove them. However, it requires a long time. Thus, development of efficient hotspot detection methods is required. As one of the methods, an existing one based on approximate string search has been proposed. Although this method is expected to find hotspots more flexibly than commonlyused template matching, computation of edit distance matrices used for approximate string search still requires a long time. Thus, in this study, we accelerate the computation by using tablereference of precomputed values and simultaneous computation of multiple elements. Our experiments showed that our improved method achieved about 1/11 computation time compared to the original one.

Keywords–lithography; hotspot; optical simulation; approximate string matching.

### I. INTRODUCTION

In nanoscale large-scale integration (LSI) manufacturing, lithography process is one of the most important processes, in which mask patterns printed on photomasks are transferred to the wafer using exposure equipment. In the process, some patterns tend to be failed to be transferred because of optical diffraction. Such patterns are called *hotspots* [1].

Since the cost of manufacturing photomasks is quite high, it is better to remove hotspots from the mask patterns in advance. Thus, lithography engineers apply optical simulation to the mask patterns received from mask designers. If hotspots are found by the optical simulation, it is informed to the designers, and the patterns are revised. This is repeated until all the hotspots are removed. However, optical simulation is timeconsuming. To reduce the number of times of optical simulation, mask designers need to detect and remove hotspots in advance. Therefore, some studies on efficient hotspot detection have been conducted [2]–[6].

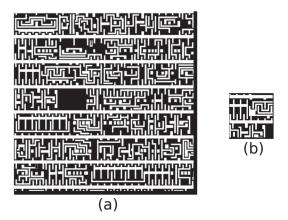

[2] proposed a template-matching-based method, which directly matches mask patterns and hotspot patterns. A mask pattern and a hotspot pattern are shown in Figure 1, as examples. A hotspot pattern is a pattern which should be detected from a mask pattern. While this method has a high ability to detect known patterns, its ability to detect unknown patterns is low. [3] discussed some hotspot detection methods using some machine-learning methods, such as artificial neural network (ANN) and support vector machine (SVM). According to the nature of machine-learning-based methods, they can detect unknown patterns as hotspots. However, they cause a large number of false-positive detections. [4] proposed a hybrid method based on template matching and machine-learning. Though the hybrid approach improved the accuracy

of detection, the number of false-positive detections is still large. In addition, it takes 10 to 100 times longer for detection. [5] adopted a fuzzy-matching model instead of ANN or SVM. They improved both of execution time of detection and the accuracy of detection. Although there exist aforementioned hotspot detection methods, some mask designers use templatematching to detect hotspot patterns since their execution time and accuracy do not meet the level required by the designers.

Figure 1. Circuit patterns: (a) mask pattern, (b) hotspot pattern

In [6], we proposed an approximate string matchingbased hotspot detection method for flexible hotspot detection. Comparing to machine-learning-based methods, this method can detect hotspot candidates in a short time. Comparing to template-matching-based methods, this method can detect hotspot candidates more flexibly (*i.e.*, unknown patterns can be detected.) However, to calculate the value of each element in the edit distance matrix for approximate string matching, we need to refer to three elements in the matrix. Thus, comparing to template-matching-based methods, in which only one value is referred for the corresponding calculation, it takes a longer time for calculation (although it is just a constant coefficient factor).

Thus, in this paper, we improve the approximate string matching-based method [6] by using table-reference of precomputed values and simultaneous calculation of multiple elements in the edit distance matrix. Each region of simultaneously handled elements is a  $k \times k$  partial matrix of the edit distance matrix, where k is the user-defined constant which decides parallelism. In the proposed method, the calculation of a region for every possible input set is performed in advance, and the result is memorized in a reference-table. Then, the edit distance matrix is calculated by using the table. For efficient calculation, the values in a region is encoded to one word of memory to calculate the values of multiple elements with only one memory access. Experimental result showed the high effectiveness of the proposed method in execution time compared to the existing method [6].

The rest of this paper is organized as follows. First, in Section II, we explain about lithography, and we provide the definitions of the approximate string matching problem, the edit distance, the approximate string search problem, which is one of the variations of the approximate string matching problem, and on which our proposing method and [6] are based. Next, in Section III, the definition of the hotspot detection problem and the existing hotspot detection method [6] are shown. Then, in Section IV, we propose an improved method which uses table-reference. Section VI shows some experimental results, and finally conclusions are given in Section VII.

### II. PRELIMINARIES

### A. Lithography

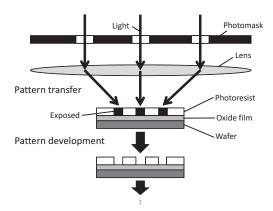

Lithography is one of the processes of LSI manufacturing. In the process, a circuit pattern drawn on a photomask is transferred to the wafer using exposure equipment. A photomask is one of the masters to make a circuit on the wafer.

Figure 2 illustrates lithography process. In lithography process, a mask pattern drawn on a photomask is transferred onto the wafer via lenses, shedding light from above the photomask. While 193nm laser is commonly used in advanced lithography processes [7], the minimum pitch between wires is decreasing, and has reached 14nm. Therefore, some subpatterns cannot be transferred correctly because of diffraction of light. Such a sub-pattern is called *a hotspot*. An example of a mask pattern is shown in Figure 3(a). The transferred image (by optical simulation) of Figure 3(a) is shown in Figure 3(b). In Figure 3(b), wires are connected at an unintended position, and some wires are too thin. Therefore, the pattern shown in Figure 3(a) is a hotspot pattern.

Figure 2. Principle of photolithography process

#### B. Approximate String Matching Problem

Approximate string matching problem [8] is one of the string matching problems, and is a problem to determine if two given strings are similar or not. In this study, the similarity between strings is measured by the edit distance explained in

Figure 3. Hotspot: (a) mask pattern, (b) its transferred image

the next subsection. If the edit distance is less than or equal to a given threshold, we consider they are similar each other.

### C. Edit Distance

Let us consider a pair of characters  $(a, b) \neq (\epsilon, \epsilon)$ , where  $\epsilon$  is an *empty character*, which represents nonexistence of any character. The operation transforming character a in a string into b is called an *edit operation*, and is denoted by  $a \rightarrow b$ . For example, let us consider a string A = gzh. If an edit operation  $q \rightarrow f$  is applied to the first character of A, we get A' = fzh as the resultant string of the operation. If an edit operation  $z \to \epsilon$  is applied to the second character of A, we get A' = gh. If an edit operation  $\epsilon \to j$  is applied to the empty character between the second and third characters of A, we get A' = qzjh. Hereinafter, we call an operation  $a \rightarrow b$  a substitution if  $a \neq \epsilon$  and  $b \neq \epsilon$ . Likewise, we call an operation  $a \to \epsilon$  a *deletion*, and call an operation  $\epsilon \to b$ an insertion. Any string can be transformed into an arbitrary string by applying the edit operations. An edit operation has its cost denoted by  $\gamma(a \rightarrow b)$ . We assume the costs of edit operations satisfy the equation below.

$$\gamma(a \to a) = 0$$

$$\gamma(a \to b) + \gamma(b \to c) \ge \gamma(a \to c)$$

Suppose strings A and B on alphabets  $\Sigma$  are given. A sequence of edit operations to transform A into B is denoted as  $O = o_1, o_2, \ldots, o_m$ . The cost of O is defined as

$$\gamma(O) = \sum_{i=1}^{m} \gamma(o_i).$$

The minimum value among the costs of all the sequences each of which transforms A into B is defined as *the edit distance between* A and B [8].

### D. Approximate String Search Problem

Approximate string search is to find substrings similar to a given pattern in a long input sequence. More precisely, approximate string search is to find all the substrings whose edit distance to the pattern P are the minimum among all the substrings (or less then the given threshold t), in the input sequence S.

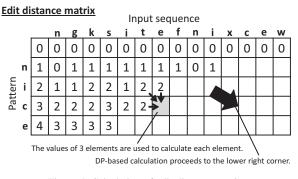

We here explain a dynamic programming-based (DP-based) algorithm for approximate string search [8], [9]. Prepare an  $(n + 1) \times (m + 1)$  two-dimensional array D, where D has n + 1 rows and m + 1 columns, n is the length of the pattern  $P = a_1 a_2 \cdots a_n$ , and m is the length of the input sequence  $S = b_1 b_2 \cdots b_m$ . An element D(i, j) (at (i+1)-th row, (j+1)-th column) of D is defined by the following equations:

$$D(0,0) = 0, \quad D(0,j) = 0,$$

$$D(i,0) = D(i-1,0) + del(a_i),$$

$$D(i,j) = \min\{ \begin{array}{c} D(i-1,j) + del(a_i), \\ D(i,j-1) + ins(b_j), \\ D(i-1,j-1) + sub(a_i,b_j) \end{array} \}$$

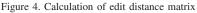

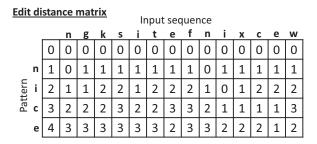

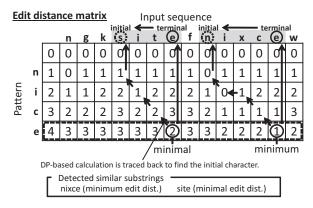

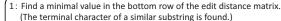

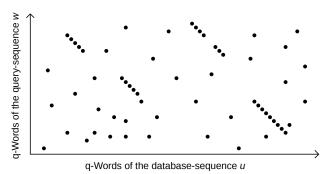

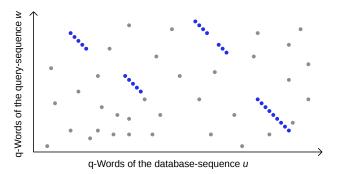

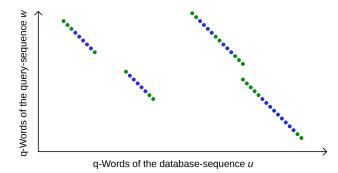

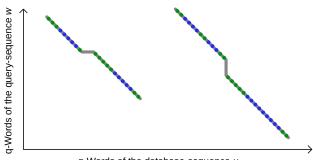

where the functions *ins*, *del*, and *sub* denote the insertion, deletion, and substitution costs. Figure 4 illustrates the DPbased calculation of an edit distance matrix, and Figure 5 shows the resultant edit distance matrix. D is called *edit distance matrix*, and  $D(n, j)(1 \le j \le m)$  gives the edit distance between the pattern P and a substring (whose terminal character is  $b_j$ ) in the input sequence S. If the value is the minimum among all the D(n, j)(j = 1, 2, ..., m) (or less than the user-defined threshold t), we consider that the substring is similar to the pattern. The initial character of such a substring is found by tracing back the DP-based calculation on D. Figure 6 illustrates how to identify similar substrings. The details of the identification of similar substrings in our proposed method are explained in Section III.

Figure 5. Edit distance matrix

### III. HOTSPOT DETECTION BASED ON APPROXIMATE STRING SEARCH

In this section, the existing hotspot detection method based on approximate string search [6], which we improve in this study, is explained. In this method, the mask pattern and a hotspot pattern, which are both two-dimensional data, are transformed into one-dimensional strings to apply approximate string search calculating array D by dynamic programming.

Figure 6. Identification of similar substrings

#### A. Transformation into One-dimensional Data

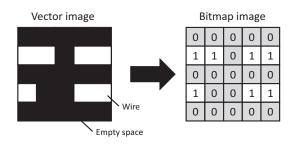

Mask patterns and hotspot patterns are image data. We transform them into two-dimensional array of characters, in which wire area is represented by 1 and empty area is represented by 0.

An example is shown in Figure 7. In the left image in it, the white areas represent wires (or other objects), and the black area represents an empty space.

Figure 7. Image data and its corresponding array

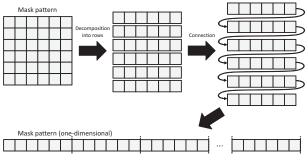

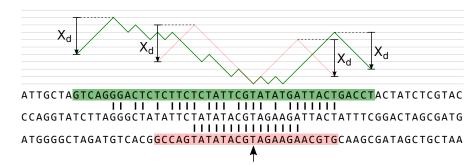

We transform the two-dimensional arrays into onedimensional data. First, the two-dimensional array of the mask pattern is divided into rows. Then, the tail of the first row and the head of the second row are connected. And, the tail of the second row is connected to the head of the third row. Likewise, all the rows are connected and the two-dimensional mask pattern is transformed into one-dimensional data (Figure 8).

Figure 8. Transformation of mask pattern data

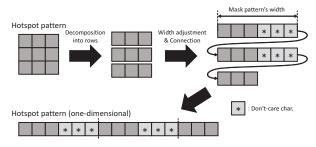

Next, the array of the hotspot pattern is divided into rows, like the transformation of the mask pattern. Then, for each row, don't-care characters are added so that the number of characters of the row becomes equal to that of a row of the mask pattern (Figure 9). A don't-care character is the special character which matches any character. By adding don't-care characters, mismatch of the positions of the head characters of the rows of the hotspot pattern is corrected. Note that such consecutive don't-care characters can be substituted by a special character, called a large-don't-care, to efficiently calculate the edit distance matrix [6]. Hereinafter, the hotspot pattern is processed just like the mask pattern.

Figure 9. Transformation of hotspot pattern data

### B. Dynamic Programming

In both of our proposed method and our previous one [6], since hotspot candidates are searched by using approximate string search, array D is calculated by using the dynamic programming shown in the previous section. Except the first row and column, the value of each element of the array D is calculated by using the value of its upper, left and upper-left elements. These calculations are done line by line from the top to the bottom.

#### C. Detection of Hotspot Candidates

After calculating array D, substrings similar to the hotspot pattern are detected as hotspot candidates. To detect hotspot candidates, we focus on the elements with the minimal values (less than a user-defined threshold) in the bottom row of D. Each of these elements is considered to correspond to the terminal character of a hotspot candidate. Since we assume the hotspot candidate has the length same as the hotspot pattern, the initial character can be identified from the terminal character. The assumption is based on the fact that a hotspot pattern and candidates similar to the pattern are originally two-dimensional images, and have the same size or almost the same size. Figure 10 illustrates an example of hotspot candidate detection of our methods. (In the example, patterns are described in regular strings for simplicity.)

### IV. PROPOSED METHOD

In this section, we propose an improved hotspot detection method based on table-reference. Our proposed method is an extension of the existing method [6]. First, we explain the basis of table-reference-based edit distance calculation, some problems for implementation, and our solutions of the problems. Then, we explain our proposed method, by describing mask pattern encoding, hotspot pattern encoding, calculation of the encoded edit distance matrix, and detection of hotspot candidates.

#### Steps of detection

2: Go back n-1 columns, where n is the length of the hotspot pattern.

(The initial character of the substring is found.)

Edit distance matrix Mask pattern inițial I terminal e f c e w k n t х 0 0 0 0 0 0 0 o 0 0 0 0 0 0 0 Hotspot pattern 0 1 1 1 1 1 1 0 1 1 1 ĺ1 1 1 1 n i 2 1 2 2 2 0 2 1 1 2 1 2 1 3 2 2 2 3 2 2 c 3 2 1 4 3 3 3 3 3 3 3 3 2 2 minimum minimal Most part of a similar substring "nixce" is covered

Figure 10. Detection of hotspot candidate

### A. Table-reference

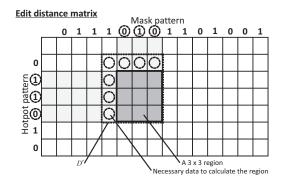

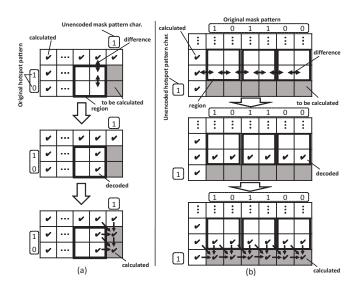

In our proposed method, calculation of the edit distance matrix is accelerated by using table-reference of precomputed values and simultaneous calculation of multiple elements in the matrix. Each region of simultaneously handled elements is a  $k \times k$  partial matrix of the edit distance matrix, where k is the user-defined constant which decides parallelism. Figure 11 shows an example of  $3 \times 3$  region. The number of inputs and outputs necessary for calculating each region is decided by k, as shown in Figure 12 (a) and (b). In addition, the values of the outputs are uniquely determined by the values of the inputs. Thus, a reference table for calculating a region can be developed. Hereinafter, a set of inputs for a table refers to an address (or index) of the table.

Figure 11. 3 x 3 region in edit distance matrix

A set of inputs for the table consists of the necessary values for DP-based calculation of the elements in a region. That is, it consists of the corresponding characters of the mask and hotspot patterns (2k characters), the k elements to the left of the region, the k elements to the upper of the region, and the element to the upper-left of the region (2k + 1 elements in total). A set of outputs consists of the values of the elements in the region. Given a region, then we call the partial matrix of D which includes the region and the elements corresponding to the inputs of the region, D' (Figure 11). D' is equivalent to the region expanded one column and one row to the upper-left direction.

However, it is not practical to directly make a table of

Figure 12. Input-output relation on the calculation of a region : (a) case of  $1 \times 1$ , (b) case of  $2 \times 2$ , (c) case of  $2 \times 2$  using the difference between adjacent elements in the edit distance (with input-output names)

region calculation, because it requires a huge memory space. This is because the range of the value of each element is large, and thus the number of combinations of the input values of the table explodes. Thus, we focus on the fact that, by deciding the reference element (e.g., the upper-left one) of D', the value of an element can be represented by the difference between the element and the reference one, and the value can be calculated by using only the differences between elements. In addition, we found the fact that the difference between the adjacent two elements is -1, 0 or 1 (when an edit cost is defined as 0 or 1). (The proof is omitted due to the limitation of space.) By adopting difference calculation considering the facts, we mitigate the virtual range of the value of each element, and thus the required memory space. Furthermore, only the values of the elements in the bottom row and the right-most column in D' are necessary for calculating the edit distance matrix D (the values of the other elements are not necessary), because only the bottom row of D is necessary for hotspot detection. Thus, the computational complexity of each region can be reduced to O(k) from  $O(k^2)$  by table-reference. Examples of sets of inputs/outputs of a table (the necessary values for calculating regions) are shown in Figure 12(c).

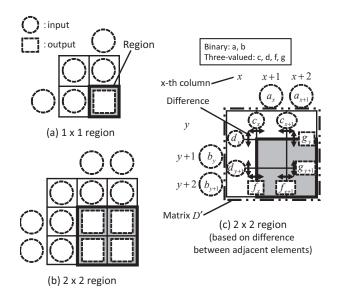

Moreover, a set of inputs/outputs can be encoded into one word when k is small. Thus, in that case, the edit distance matrix can be calculated in the encoded values, so that the computational complexity of each region is reduced to O(1)from O(k). Figure 13 illustrates encoded inputs and outputs.

Let (x, y) be the coordinate of the upper-left element of D' in the edit distance matrix D. Then, the inputs are

- $a_x, a_{x+1}, ..., a_{x+(k-1)}$ : mask pattern characters corresponding to the region (input1)

- $b_y, b_{y+1}, ..., b_{y+(k-1)}$ : hotspot pattern characters corresponding to the region (input2)

- c<sub>x</sub>, c<sub>x+1</sub>, ..., c<sub>x+(k-1)</sub>: the differences between adjacent two elements in the upper-most row of D' (in-put3)

- $d_y, d_{y+1}, \dots, d_{y+(k-1)}$ : the differences between adja-

Figure 13. Encoding of inputs/outputs of region: (a) unencoded inputs/outputs of  $2 \times 2$  region, (b) encoded inputs/outputs

cent two elements in the left-most column of D' (input4),

and the outputs are

- $f_x, f_{x+1}, \dots, f_{x+(k-1)}$ : the differences between adjacent two elements in the bottom row of D' (output1)

- $g_y, g_{y+1}, \dots, g_{y+(k-1)}$ : the differences between adjacent two elements in the right-most column of D' (output2).

The inputs/outputs are encoded by the encoding functions

$$P(p_x, p_{x+1}, \dots, p_{x+i}) = \sum_{i=0}^{k-1} p_{x+i} \times 2^{(k-1)-i}$$

(1)

$$Q(q_x, q_{x+1}, ..., q_{x+i}) = \sum_{i=0}^{k-1} q_{x+i} \times 3^{(k-1)-i}$$

(2)

to develop a table.

Hereinafter, we call the four inputs, input1, input2, input3, and input4, and the two outputs, output1 and output2. The ones composed of binary variables are encoded by using (1), and the ones composed of three-valued (-1, 0, 1) variables are encoded by using (2). Therefore, the outputs can be memorized in two words of memory if  $\log_2 3^k$  is less than or equal to the bit width of a word. In that case,  $k \times k$ -element calculation can be done accessing the memory only two times, so that the computational complexity of each region is O(1). Note that the number of possible combinations of the inputs is  $2^{2k} \times 3^{2k}$  and is an exponential function of k. In our experimental environment, we developed tables up to k = 5 (0.23GB).

### B. Hotspot detection using table-reference

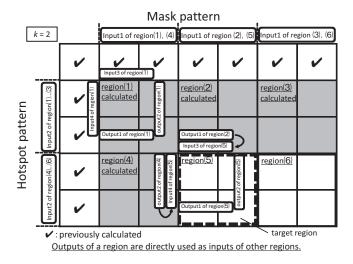

In this subsection, we explain our table-reference-based hotspot detection method. As mentioned in the previous subsection, a table is developed by calculating the output values of a region for each possible combination of input values before starting hotspot detection. Then, the table is used for efficient hotspot detection.

1) Pattern encoding: The mask and hotspot patterns in two-dimensional arrays are transformed into one-dimensional strings in the same way as [6]. Next, the mask and hotspot patterns are divided into k-character substrings and then each substring is encoded to use the reference table for calculating the edit distance matrix. Note that, in the hotspot pattern, since large don't-care characters cannot be calculated in the encoded

form, large don't-care characters are not encoded, and thus they are not included in a k-character substrings. Each k-character substring is encoded by using (1). The terminal substring (of the mask pattern) whose length are less than k is left as an unencoded string. Likewise, in the hotspot pattern, large don'tcare characters and the substrings whose length are less than k (including those resulting from the inserted large don't-care characters) are left as unencoded strings.

2) Calculation of edit distance matrix D: Using the encoded patterns, the calculation of the edit distance matrix D is performed by referencing the table. Let us explain the calculation using Figure 14. First, the values of the element of the first row and column are set according to the definition of the edit distance matrix. Next, the region whose upperleft element corresponding to the element D(1,1) (region (1)) is calculated by table-reference. After calculating region (1), the region adjacent to the right of region (1) (region (2)) is calculated. Let region (5) be an example. The input3 of region (5) is from the output1 of region (3), and the input4 of region (5) is from the output2 of region (4). In this way, the encoded outputs of regions can be directly used as inputs to calculate other regions. After table-reference-based calculation, the values of the elements in the bottom row of the edit distance matrix D can be restored by using the value of the left-most element and the differences between adjacent two elements obtained by decoding the output1 of each bottom region.

Figure 14. Calculation of edit distance matrix by table reference

We have explained the edit distance calculation ignoring unencoded substrings. Here, let us explain how to handle unencoded mask pattern substrings using Figure 15(a). First, the output2 of the region just before the unencoded mask pattern character is decoded to the differences between adjacent elements in the corresponding column. Next, the values of the elements are restored using the value of the upper-most element and the differences between elements. Then, the values of the elements corresponding to the unencoded substrings are calculated according to the DP-based definition in the same way as [6].

Next, let us explain how to handle unencoded hotspot pattern substrings using Figure 15(b). First, the output1s of the regions just above the unencoded hotspot pattern character are decoded to the differences between adjacent elements in the corresponding row. Next, the values of the elements are restored using the value of the left-most element and the differences between elements. Then, the values of the elements corresponding to the unencoded substrings are calculated according to the DP-based definition in the same way as [6]. Also the substrings before the large don't-care characters are handled in the same way. Since each row of hotspot pattern (in a two-dimensional hotspot pattern) means one large don'tcare character, a hotspot pattern string contains multiple large don't-care characters. This calculation is performed for each large don't-care character.

Figure 15. Calculation for unencoded character: (a) mask pattern character, (b) hotspot pattern character

Finally, if the hotspot pattern character corresponding to the bottom row is encoded, the values of the elements in the bottom row of the edit distance matrix D are restored to find hotspot candidates. If the hotspot pattern character is not encoded, the values of the elements in the bottom row of Dare calculated according to the definition as mentioned in the previous paragraph.

3) Detection of similar patterns: After calculating the edit distance matrix D, patterns similar to the hotspot pattern are detected from the values of the bottom row of D. The elements with minimal values (less than the user-defined threshold) are identified in the same way as [6]. Each of them corresponds to the terminal character of a hotspot candidate. The initial character can be identified by the terminal character because the length of a hotspot candidate is the same as the given hotspot pattern.

### V. EXPERIMENTAL RESULTS

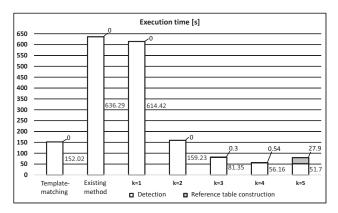

We performed experiments to evaluate our method. In the experiments, we evaluated the execution time of templatematching, the existing method [6], and our proposed method for k = 1, ...5, for the same mask pattern (1020 × 1020 pixels) and the same hotspot pattern (250 × 250 pixels), on a CentOS (release 6.3 (Final)) PC equipped with Intel Core i7-3770 CPU @ 3.4GHz and 7.6GB memory using gcc 4.4.7.

The experimental results are shown in Figure 16. Our proposed method achieved the better result compared to [6]

Figure 16. Calculation time

for each setting of k. When  $k \ge 3$ , our method outperformed template-matching. We confirmed that the calculation time of the edit distance matrix D was drastically reduced.

The calculation time of D is inversely proportional to  $k^2$ . Thus, it is expected that the decreasing rate of the calculation time decreases with increasing k. In addition, the time to make the reference table is proportional to the number of combinations of input values (*i.e.*,  $2^{2k} \times 3^{2k}$ ). That is, the time is proportional to an exponential function of k. Therefore, from Figure 16, the sum of the time to make the reference table and the time to calculate D increases when  $k \ge 5$ . Thus, we conclude that k = 4 is best under the experimental environment. The execution time when k = 4 was about 1/11 compared to the existing method [6]. Note that once a reference table is made, it can be reused. In such a case,  $k \ge 5$ are potentially effective.

### VI. CONCLUSIONS

In this paper, we proposed and evaluated an efficient hotspot detection method. Experimental results showed that our proposed method found hotspot candidates much faster than the existing one [6] on which our method is based. Our future work includes further improvement of the execution time and improvement of the accuracy of hotspot detection.

#### REFERENCES

- T. Higashi and Y. Onishi, "Trends in semiconductor lithography technologies and Toshiba's approach," TOSHIBA review, vol. 67, no. 4, pp. 2-6, 2012. (in Japanese)

- [2] H. Yao et al., "Efficient range pattern matching algorithm for processhotspot detection," IET Circuits Devices Syst., vol. 2, issue 1, pp. 2–15, 2008.

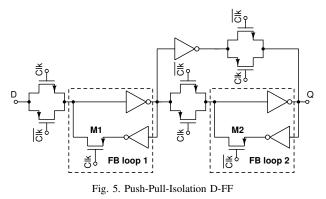

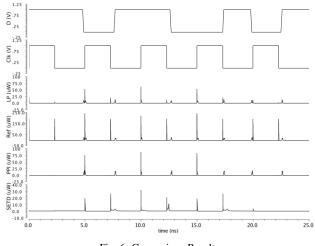

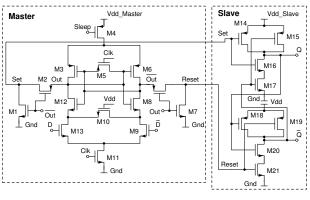

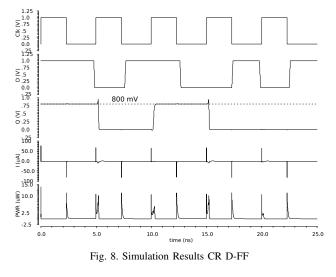

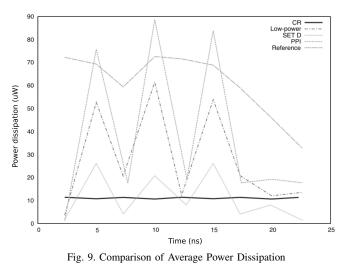

- [3] D. Ding, A. J. Torres, F. G. Pikus, and D. Z. Pan, "High performance lithographic hotspot detection using hierarchically refined machine learning," in Proc. the 16th Asia and South Pacific Design Autom. Conf. (ASP-DAC), pp. 775–780, 2011.