# **CENICS 2019**

The Twelfth International Conference on Advances in Circuits, Electronics and Micro-electronics

ISBN: 978-1-61208-748-1

October 27 - 31, 2019

Nice, France

# **CENICS 2019 Editors**

Sandra Sendra, Universidad de Granada, Spain Pascal Lorenz, University of Haute Alsace, France

# **CENICS 2019**

# Forward

The Twelfth International Conference on Advances in Circuits, Electronics and Micro-electronics (CENICS 2019), held between October 27, 2019 and October 31, 2019 in Nice, France, continued a series of events initiated in 2008, capturing the advances on special circuits, electronics, and micro-electronics on both theory and practice, from fabrication to applications using these special circuits and systems. The topics covered fundamentals of design and implementation, techniques for deployment in various applications, and advances in signal processing.

Innovations in special circuits, electronics and micro-electronics are the key support for a large spectrum of applications. The conference is focusing on several complementary aspects and targets the advances in each on it: signal processing and electronics for high speed processing, micro- and nanoelectronics, special electronics for implantable and wearable devices, sensor related electronics focusing on low energy consumption, and special applications domains of telemedicine and ehealth, bio-systems, navigation systems, automotive systems, home-oriented electronics, bio-systems, etc. These applications led to special design and implementation techniques, reconfigurable and self-reconfigurable devices, and require particular methodologies to be integrated on already existing Internet-based communications and applications. Special care is required for particular devices intended to work directly with human body (implantable, wearable, ehealth), or in a human-close environment (telemedicine, house-oriented, navigation, automotive). The mini-size required by such devices confronted the scientists with special signal processing requirements.

We take here the opportunity to warmly thank all the members of the CENICS 2019 technical program committee, as well as all the reviewers. The creation of such a high quality conference program would not have been possible without their involvement. We also kindly thank all the authors who dedicated much of their time and effort to contribute to CENICS 2019. We truly believe that, thanks to all these efforts, the final conference program consisted of top quality contributions.

We also thank the members of the CENICS 2019 organizing committee for their help in handling the logistics and for their work that made this professional meeting a success.

We hope that CENICS 2019 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in the field of circuits, electronics and micro-electronics. We also hope that Nice, France provided a pleasant environment during the conference and everyone saved some time to enjoy the charm of the city.

#### **CENICS 2019 Chairs**

### **CENICS Steering Committee**

Falk Salewski, Muenster University of Applied Sciences, Germany Chun-Hsi Huang, University of Connecticut, USA Diego Ettore Liberati, National Research Council of Italy, Italy Julio Sahuquillo, Universitat Politècnica de València, Spain Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Bartolomeo Montrucchio, Politecnico di Torino, Italy Petr Hanáček, Brno University of Technology, Czech Republic

### **CENICS Research/Industry Committee**

John Vardakas, Iquadrat Informatica, Barcelona, Spain Laurent Fesquet, TIMA laboratory | Grenoble Institute of Technology, France Christian Wögerer, PROFACTOR GmbH, Austria Miroslav Velev, Aries Design Automation, USA Ivo Stachiv, Institute of Physics | Czech Academy of Sciences, Prague, Czech Republic / Harbin Institute of Technology | Shenzhen Graduate School, Shenzhen, China Amir Shah Abdul Aziz, TM Research & Development, Malaysia

## CENICS 2019 Committee

### **CENICS Steering Committee**

Falk Salewski, Muenster University of Applied Sciences, Germany Chun-Hsi Huang, University of Connecticut, USA Diego Ettore Liberati, National Research Council of Italy, Italy Julio Sahuquillo, Universitat Politècnica de València, Spain Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Bartolomeo Montrucchio, Politecnico di Torino, Italy Petr Hanáček, Brno University of Technology, Czech Republic

## **CENICS Research/Industry Committee**

John Vardakas, Iquadrat Informatica, Barcelona, Spain Laurent Fesquet, TIMA laboratory | Grenoble Institute of Technology, France Christian Wögerer, PROFACTOR GmbH, Austria Miroslav Velev, Aries Design Automation, USA Ivo Stachiv, Institute of Physics | Czech Academy of Sciences, Prague, Czech Republic / Harbin Institute of Technology | Shenzhen Graduate School, Shenzhen, China Amir Shah Abdul Aziz, TM Research & Development, Malaysia

## **CENICS 2019 Technical Program Committee**

Francesco Aggogeri, University of Brescia, Italy Adel Al-Jumaily, University of Technology, Sydney, Australia Mohammad Amin Amiri, Malek Ashtar University of Technology, Islamic Republic of Iran Patroklos Anagnostou, Leclanché SA, Switzerland Nihar Athreyas, Spero Devices, Inc., USA Amir Shah Abdul Aziz, TM Research & Development, Malaysia Payman Behnam, University of Utah, USA Fayçal Bensaali, Qatar University, Qatar Vincent Beroulle, Grenoble INP (Institute of Engineering Univ. Grenoble Alpes), France Timm Bostelmann, FH Wedel (University of Applied Sciences), Germany Hamza Bouzeria, Constantine - 1- University, Algeria Khalid Bouziane, Université Internationale de Rabat, Morocco Luca Calderoni, University of Bologna, Italy David Cordeau, XLIM UMR CNRS 7252, France Nicola D'Ambrosio, Laboratori Nazionali del Gran Sasso (LNGS) – INFN, Italy Jamal Deen, Academy of Science - Royal Society of Canada / McMaster University, Canada Javier Diaz-Carmona, Technoligical Institute of Celaya, Mexico Alie El-Din Mady, United Technologies Research Center, Cork, Ireland Diego Ettore Liberati, National Research Council of Italy, Italy Maher Fakih, OFFIS e.V. Institut für Informatik, Oldenburg, Germany Francisco Falcone, ISC-UPNA, Spain

Paulo Felisberto, LARSyS | University of Algarve, Portugal Laurent Fesquet, Grenoble Institute of Technology, France Kelum Gamage, Glasgow University, UK Alexander Gelbukh, Instituto Politécnico Nacional, Mexico Patrick Girard, LIRMM, France Alfonso Gómez-Espinosa, Tecnologico de Monterrey, Mexico Amir M. Hajisadeghi, Amirkabir University of Technology (Tehran Polytechnic), Iran Petr Hanáček, Brno University of Technology, Czech Republic Cong Hao, University of Illinois, Urbana-Champaign, USA Abdus Sami Hassan, Chosun University, Korea Houcine Hassan, Universitat Politècnica de València, Spain Chun-Hsi Huang, University of Connecticut, USA Jose Hugo Barron-Zambrano, Universidad Autonoma de Tamaulipas, Mexico Wen-Jyi Hwang, National Taiwan Normal University, Taiwan Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Eric Kerherve, IMS Laboratory, France Oliver Knodel, Technische Universität Dresden, Germany Ulrich Kühne, Télécom ParisTech, France Yazhu Lan, Duke University, USA Junghee Lee, Korea University, Korea Kevin Lee, Nottingham Trent University, UK Yo-Sheng Lin, National Chi Nan University, Taiwan David Lizcano, Madrid Open University (UDIMA), Spain Rabi N. Mahapatra, Texas A&M University, USA Sachin Maheshwari, University of Westminster, London, UK Cristina Meinhardt, Federal University of Rio Grande (FURG), Brazil Harris Michail, Cyprus University of Technology (CUT), Cyprus Amalia Miliou, Aristotle University of Thessaloniki, Greece Georgi Mladenov, Bulgarian Academy of Sciences | Institute of electronics, Bulgaria Jose Manuel Molina Lopez, Universidad Carlos III de Madrid, Spain Bartolomeo Montrucchio, Politecnico di Torino, Italy Rafael Morales Herrera, University of Castilla-La Mancha, Spain Ioannis Moscholios, University of Peloponnese, Greece Shinobu Nagayama, Hiroshima City University, Japan Arnaldo Oliveira, UA-DETI/IT-Aveiro, Portugal Vittorio M.N. Passaro, Politecnico di Bari, Italy Nikos Petrellis, TEI of Thessaly, Greece Marc Porti, Universitat Autònoma de Barcelona, Spain Himadri Singh Raghav, University of Westminster, London, UK Ahmad Razavi, University of California, Irvine, USA Càndid Reig, University of Valencia, Spain Piotr Remlein, Poznan University of Technology, Poland Brian M. Sadler, Army Research Laboratory, Adelphi, USA Djohra Saheb, Centre de Développement des Energies Renouvelables (CDER), Algeria Julio Sahuquillo, Universitat Politècnica de València, Spain Amgad A. Salama, ADRC, Egypt Falk Salewski, Muenster University of Applied Sciences, Germany Sergei Sawitzki, FH Wedel (University of Applied Sciences), Germany

Sandra Sendra, Universidad de Granada, Spain Emilio Serrano, Universidad Politécnica de Madrid, Spain Rishad Shafik, Newcastle University, UK Muhammad Shafique, Vienna University of Technology, Austria Mustafa M. Shihab, The University of Texas at Dallas, USA Saeideh Shirinzadeh, University of Bremen, Germany Ashif Sikder, Ohio University, USA Sharad Sinha, Indian Institute of Technology (IIT), Goa, India Kenneth Skovhede, University of Copenhagen, Denmark Ivo Stachiv, Institute of Physics | Czech Academy of Sciences, Prague, Czech Republic / Harbin Institute of Technology | Shenzhen Graduate School, Shenzhen, China Francisco Torrens, Universitat de Valencia, Spain Carlos M. Travieso-González, Universidad de Las Palmas de Gran Canaria, Spain John Vardakas, Iquadrat Informatica, Barcelona, Spain Miroslav Velev, Aries Design Automation, USA Manuela Vieira, ISEL-CTS-UNINOVA, Portugal Jin Wei, University of Akron, USA Robert Wille, Institute for Integrated Circuits | Johannes Kepler University, Linz, Austria Christian Wögerer, PROFACTOR GmbH, Austria Pengcheng Xu, UCLouvain, Belgium Ravi M Yadahalli, SG Balekundri Institute of Technology, India Lei Yang, Chongqing University, China / University of Pittsburgh USA Dan Zhang, York University, Toronto, Canada Piotr Zwierzykowski, Poznan University of Technology, Poland

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

## **Table of Contents**

| VHDL Design Tool Flow for Portable FPGA Implementation<br>Vijaykumar Guddad, Alexandra Kourfali, and Dirk Stroobandt                                                         | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Implementation of an FPGA - Raspberry Pi SPI Connection<br>Haissam Hajjar and Hussein Mourad                                                                                 | 7  |

| Accelerating FPGA-Placement With a Gradient Descent Based Algorithm<br>Timm Bostelmann, Tobias Thiemann, and Sergei Sawitzki                                                 | 13 |

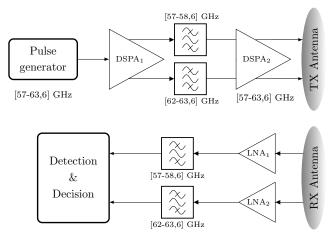

| 60 GHz Low-Noise Amplifier in a 70 nm GaAs m-HEMT Technology for Multi-band Impulse Detection System Pape Sanoussy Diao, Thierry Alves, Benoit Poussot, and Martine Villegas | 19 |

| A Convolutional Neural Network Accelerator for Power-Efficient Real-Time Vision Processing Junghee Lee and Chrysostomos Nicopoulos                                           | 25 |

## **VHDL Design Tool Flow for Portable FPGA Implementation**

Vijaykumar Guddad, Alexandra Kourfali and Dirk Stroobandt ELIS department, Computer Systems Lab, Ghent University iGent, Technologiepark Zwijnaarde 126, B-9052 Ghent - Belgium Email: {Vijaykumar.Guddad, Alexandra.Kourfali, Dirk.Stroobandt}@UGent.be

Abstract-In Field-Programmable Gate Array (FPGA) design, the coding style has a considerable impact on how an application is implemented and how it performs. Many popular Very-High-Speed Integrated Circuits Hardware Description Language (VHDL) logic synthesis tools like Vivado by Xilinx, Quartus II by Altera, and IspLever by Lattice Semiconductor, have significantly improved the optimization algorithm for FPGA synthesis. However, the designer still has to generate synthesizable VHDL code that leads the synthesis tools and achieves the required result for a given hardware architecture. To meet the required performance, VHDL based hardware designers follow their own rules of thumb, and there are many research papers which suggest best practices for VHDL hardware designers. However, as many trade-offs have to be made and results depend on the combination of optimized implementations and optimized hardware architectures, final implementation decisions may have to change over time. In this paper, we present a VHDL design tool flow that makes portability of the design to new design requirements easier. It helps to generate automated portable VHDL design implementations and customized portable VHDL design implementations. This tool flow helps the VHDL hardware designers to generate a single VHDL design file, with multiple design parameters. It also helps the end-users of VHDL hardware designs in choosing the right parameter settings for a given hardware architecture and generating the right bit file corresponding to these parameter settings, according to their requirements.

Keywords-FPGA; VHDL; Toolflow; VIVADO.

#### I. INTRODUCTION

Field-Programmable Gate Arrays (FPGAs) are attractive platforms for custom hardware implementation. They have been used in accelerating high-performance applications in which the complexity is significantly reduced by employing custom hardware to parts of the problem. They have been attractive for many new applications in which their flexibility and configurability are in high demand. The FPGA's strength comes from the fact that hardware developers can program it to deliver exactly what they need for their design, and massive spatial parallelism at low energy gives FPGAs the potential to be core components in large scale High-Performance Computing (HPC).

Very-High-Speed Integrated Circuits Hardware Description Language (VHDL) is a Hardware Description Language (HDL) that is used to program FPGAs. It describes the behaviour of an electronic circuit or system, from which the physical circuit or system can then be implemented. FPGAs work on configuration bits that define the functionality. To generate configuration bits from HDL, an FPGA tool flow is used. An FPGA tool flow aims to produce a configuration for the target FPGA that implements the functionality described in the HDL design. The current FPGA tool flow consists of synthesis, technology mapping, packing placement and routing. In the synthesis step, the HDL code is translated from a humanreadable form to a gate-level logic circuit. The synthesis tool is also responsible for optimising the circuits depending on the needs of the designer. During technology mapping, the gatelevel circuit generated by the synthesis step is mapped onto the resource primitives (ex. Lookup tables (LUTs), Flipflops (FFs), DSP blocks (DSPs), BlockRAMs) available in the target FPGA architecture. In packing, LUT primitives and FFs from the mapped netlist are clustered into Configuration Logic Blocks (CLBs) according to their interconnectivity. During placement and routing, CLBs are assigned to physical logic blocks on the FPGA, and these CLBs are connected using switch blocks and wires. Finally, the configuration bitstream is generated. Recently, increasing research has been performed in the field of placement and routing, and also commercial FPGA tools (Vivado by Xilinx, Quartus II by Altera, IspLever by Lattice Semiconductor, Encounter RTL compiler by Cadence Design Systems, LeonardoSpectrum, Precision by Mentor Graphics, and Synplify by Synopsys) optimised their algorithm for better results [1]-[3].

The tool flow proposed in this paper is mainly related to targetting the synthesis step. The coding style can have a severe impact on the resource utilisation of an FPGA architecture. and how it performs on the target board. The designer can write HDL code that forces the synthesis step to make use of available FPGA resources or not to use the specific resources. The designer can also write HDL code that has higher or lower throughput or a different design operating frequency. There are many research papers and books [4]–[6] which suggest best practices and techniques; also, each commercial FPGA vendor has their own coding guidelines [7] [8]. Apart from all these guidelines, each designer and company follows their own rules of thumb in order to achieve the required results according to the design requirements. These techniques and guidelines are specific to the particular FPGA architecture and model. As we can see in the current market, FPGA architectures and models keep changing to fulfill a new market need (e.g., currently, most FPGA vendors are designing their boards to target machine learning, deep neural networks, and data server requirements). From the above discussion, we can categorize these coding techniques and methods into three main categories: i) technology independent coding styles, ii) performance driven coding, iii) technolonology specific coding techniques.

In this paper, we present a method to combine all possible coding techniques, methods, and rules of thumb in a single VHDL design file. The tool flow processes the VHDL design file with all possible techniques, methods, and rules of thumb, which is independent of the FPGA vendor and the architecture. In Section II and Section III, we present different types of VHDL coding techniques and methods and describe a method to combine all possible techniques in a single VHDL design file. In Section IV, we present the portable tool flow integrated with a synthesis tool to process input VHDL design files. In Section V, we give results and a conclusion.

#### II. VHDL CODING TECHNIQUES AND METHODS

In this section, we will discuss three main coding techniques and methods with an example. In the end, we describe a method to combine these techniques and methods in a single VHDL design file.

#### A. Technology independent coding styles

As the name suggests, technology independent coding techniques are independent of the FPGA architecture, vendor, and technology. Here, we will discuss a few techniques [9]–[12].

1) Sequential devices design techniques: In sequential devices, we have two main types of memory devices: a latch and a flip-flop. A latch is a level-sensitive memory device and a flip-flop is an edge triggered memory device [3] [13].

*Data-Latches:* Here we will see different ways, of using Data-latches (D-latches).

D-Latch with data and enable:

#### begin

```

process (enable, data) begin

if (enable= '1') then

y<=data;</pre>

```

D-Latch with gated asynchronous data:

```

process (enable, gate, data) begin

if (enable = '1') then

q <= data and gate;</pre>

```

D-Latch with gated enable:

```

process (enable, gate, d) begin

if ((enable and gate) = '1') then

q <= d;</pre>

```

D-Latch with asynchronous reset:

```

process (enable, data, reset) begin

if (reset = '0') then

q <= '0';

elsif (enable = '1') then

q <= data;</pre>

```

2) Datapath: Datapath logic is a structured repetitive function. These structures can be modelled in a different implementation depending upon timing and area constraints. The following synthesis tools generate optimal implementations for the target technology depending upon the datapath model used in the VHDL code [9] [13].

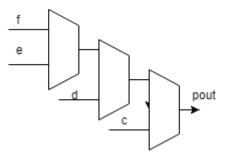

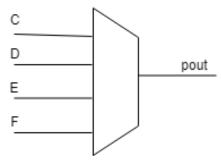

(i) Using if-then-else and case statement: An if-then-else statement is used to execute sequential statements based on a condition. Each of the if-then-else statements is checked until a true condition is found. Statements associated with a true condition are executed and the rest of the statement is ignored. Using if-then-else statements in VHDL code forces synthesis tools to realize the circuit in a way shown in Figure 1.

A case statement implies parallel encoding and a case statement is used to select one of several alternative statement

Figure 1. Effect on synthesis tool using an if-then-else statement

sequences based on the value of a condition. The condition is checked against each choice in the case statement until the match is found. Using case statements in VHDL code forces synthesis tools to realise the circuit in a way shown in Figure 2.

Figure 2. Effect on synthesis tool using a case statement

While writing VHDL code, it is difficult to predict how using an if-then-else statement or a case statement will effect the critical path of the final design or the design throughput or design requirements. The optimisation level of each statement varies from one synthesis tool to the other. In such cases, we can define both statements in a VHDL design file using the keyword - -# using\_case and - -#using\_if\_else. Later, we can make choices at the synthesis step depending upon requirements using the tool flow presented in the next section.

(ii) Designing Multiplexers: While writing VHDL code, we can force the synthesis tool to make use of 4:1 or 6:1 or 12:1mux. The LUT inputs vary with the architecture, thus optimizing for different mux types can affect the synthesis to architecture step [10] [14].

(iii) Counters: Counters count the number of occurrences of an event that occurs either at regular intervals or randomly. Counters can be designed in one of the following ways: i) a counter with count enable and asynchronous reset, ii) a counter with load and asynchronous reset, and iii) a counter with load, count enable, and asynchronous reset. However, most synthesis tools cannot find the optimal implementation of counters higher than 8- bits. If the counter is in the critical path of a speed and area critical design, it is better to redesign using one of the ways mentioned above or to use a pre-instantiated counter provided by the vendor [9] [10].

3) Input-output buffers: We can infer or instantiate an Input/Output buffer in the VHDL design depending upon design requirements. The usage of inference and instantiation

Figure 3. Example circuit designs

has its own advantages and disadvantages. For example, in the inference method, we define a tri-state buffer using an entity port in the design, whereas in the instantiation method, we make use of the tristate component design provided by synthesis tools [4] [9].

#### B. Performance driven coding

In the FPGA, each logic level used in the design path can add a delay. As a result, meeting timing and area constraints on a critical path with many logic levels becomes difficult. Using an efficient coding style is important because it dictates the synthesis logic implementation. In this section, we will discuss a few essential techniques [9] [15].

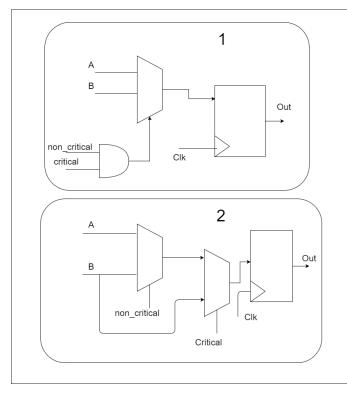

1) Reducing logic levels on critical paths: Consider a small circuit design, as shown in Figure 3. Here, we have two circuit designs with the same functionality but designed differently.

In circuit 1 of Figure 3, the signal "critical" goes through two logic gates.

```

if (clk'event and clk ='1') then

if (non_critical and critical) then

out1 <= A

else

out1 <= B

end if;

end if;</pre>

```

To reduce the logic gate usage on "critical" signals, multiplex inputs "A" and "B" based on "non\_critical" and call this output "out\_temp". Then multiplex "out\_temp" and "B" based on "critical". As a result, the signal "critical" goes through one logic gate as shown in circuit 2 of Figure 3.

2) Resource sharing: The resource sharing technique is used to reduce the number of logic modules needed to implement VHDL operations. Here, we have two pieces of VHDL code: one makes use of four adders and another uses two adders.

```

--Example implementation with 4 Adders

if (...(siz == 1)...)

count = count + 1;

else if (...(siz ==2)...)

count = count + 2;

else if (...(siz == 3)...)

count = count + 3;

else if (...(siz == 0)...)

count = count + 4;

--Example implementation with 2 Adders

if (...(siz == 0)...)

count = count + 4;

else

count = count + 4;

```

#### C. Technology specific coding techniques

These coding techniques are used to take advantage of the specific FPGA architecture, to improve speed and area utilization of the design. These techniques have their own coding guidelines to take advantage of their FPGA architectures [8] [16].

# III. METHOD TO COMBINE ALL POSSIBLE DESIGN TECHNIQUES IN A SINGLE VHDL DESIGN FILE

From the above discussions, we observe that the VHDL coding style has a considerable impact on how an FPGA design is implemented, and ultimately, how it performs. Here, we present a method to combine all possible VHDL design methods and techniques in a single design file. Let us consider a VHDL design file where we have two processes in a behavioral architecture and each process has to be described with different pipeline stages. Later, before the synthesis step, we plan to select the pipeline stages between each process, and a method to combine this would be as follows:

```

architecture behavioral of <identifier> is

begin

process(<signal>)

-- Process 1

begin

--#pipelined=0

-- < code>

--#pipelined=0

--#pipelined=1

< code >

--#pipelined=1

process(<signal>)

--Process 2

begin

--#pipelined=0

< code>

```

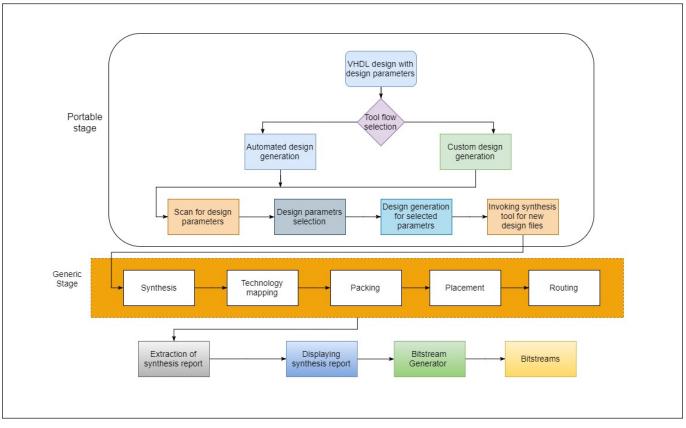

Figure 4. VHDL design tool flow for portable FPGA implementation

--#pipelined=0 --#pipelined=1 -- < code > --#pipelined=1

Here, we make use of the keyword "- -#" followed by a design parameter instance. We can use this keyword to define any part of the code like input-output ports, signals, or the architecture part of the code. We can use any possible name to define the design parameter instance and there is no syntax rule for the names. The only condition we put forward for different parameter design parts is that they should start and end with the same design parameter name (from the above code design, a parameter means -#pipelined=1, -#pipelined=2). From the above code, we can observe in process 1 we commented the pipelined=0 and kept the pipelined=1 as default. In process 2, we kept pipelined=0 as default. It will help in processing the design files without our tool flow.

#### IV. VHDL DESIGN TOOL FLOW FOR PORTABLE DESIGN GENERATION

As seen in Section III, now we have a way to combine multiple design techniques and methods in a single VHDL design file. However, this type of VHDL design file cannot be synthesised by regular synthesis tools. Therefore, we need a tool flow which can guide the synthesis tool in implementing combined VHDL design files, and which can allow the user to decide and generate portable VHDL designs.

In Figure 4, we present our proposed tool flow. As it can be observed, the tool flow is designed in two stages: the portable stage and the generic stage. The portable stage processes the input design files and allows the user to make the selection between different design parameters. The generic stage processes the new design files generated by the portable stage and generates a synthesis report and a bit-file.

In the portable stage, the tool flow receives the input design files. The tool flow scans for the design parameters available in the design files and prints them to the user. Then, the tool flow allows the user to select either automated design or customised design. In the automated design, the user can apply a selected set of design parameters or techniques to all available design files. In the customised design selection, the user can choose between different design files, for using selected design parameters. After successful selection of the design parameters available from the input design files, the tool flow searches for the user selected design parameters in each design file and extracts the design parameter content from each design file. If the user selected design parameter does not match with parameters in the design file, the tool flow will keep the default design parameter. After this the tool flow generates the new design files. The newly generated design files are processed further with the generic stage to generate a synthesis report. Next, the synthesis report is extracted and displayed to the user, and finally, the bit-file is generated. The portable tool flow proposed in this paper is independent of the used FPGA architecture. This can be integrated with any FPGA architecture, just by changing the invoking statement in the code. For example, to invoke the Xilinx Vivado design suite, the following code is used:

#### vivado-mode batch -source design.tcl

One can think it is a lot of manual work to define all possible design parameters in a design file, but as we discussed in the introduction, our idea is to combine all possible coding techniques, methods, and rules of thumb in a single design file. It is easier for a designer to propose different smaller design options in sub-parts of the design than to provide different complete designs full of different choices. So the designer does not have to worry about how different choices are combined (as this is done automatically) but can focus on the individual different options. This is a huge difference.

#### V. RESULTS AND DISCUSSION

In this section, we will evaluate the portable VHDL design tool flow and present the results [17]. In our experiments, we used an 8 core CPU system. We integrated our portable VHDL design tool flow with the Xilinx synthesis tool (Vivado 2018.3) [18], to generate the synthesis report and the bit-file.

# A. Evaluating the portable VHDL design tool flow for a single design file (using technology independent coding styles)

Here, we considered the data flip-flop VHDL design file with seven design parameters (techniques) in a single VHDL design file. We compared our results with the standard VHDL design with a single design parameter. These results are tabulated in Table I.

TABLE I. RESULTS USING PORTABLE VHDL DESIGN TOOL FLOW AND GRAPHICAL USER INTERFACE OF SYNTHESIS TOOL

|                | Design<br>parameters<br>available | Time taken<br>to write<br>design file<br>in Minutes<br>(aprox) | Time required to<br>edit for other design<br>parameters in<br>Minutes (aprox) | Space<br>required to<br>store design<br>file | Time to run<br>synthesis for<br>all parameters |  |  |

|----------------|-----------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------|--|--|

|                |                                   | Without uisng portable tool flow                               |                                                                               |                                              |                                                |  |  |

| Data flip-     | 1                                 | 3 Min                                                          | 15 Min                                                                        | 4.00 KB                                      | 20 Min                                         |  |  |

| flop<br>design |                                   | Using portable tool flow                                       |                                                                               |                                              |                                                |  |  |

|                | 7                                 | 7 Min                                                          | 0 Min                                                                         | 7.02 KB                                      | 10 Min                                         |  |  |

From Table I, we can observe that we have two different implementation results: one using our portable VHDL design tool flow, and another one using the Graphical User Interface (GUI) of Vivado design suite. In this experiment, we considered the seven design techniques (parameters) to design a data flip-flop. These are i) rising edge flip-flop, ii) rising edge flip-flop with asynchronous reset, iii) rising edge flipflop with asynchronous preset, iv) rising edge flip-flop with asynchronous reset, v) rising edge flip-flop with synchronous reset, vi) rising edge flip-flop with synchronous reset, vi) rising edge flip-flop with synchronous preset, vii) rising edge flip-flop with asynchronous reset and clock enable. While using the GUI, we designed the data flip-flop considering one design technique at a time and subsequently edited the design for other parameters to get the corresponding synthesis report and the bit-file. In the second instance, we used the portable VHDL design tool flow, combining all techniques in a single design file and generating the synthesis report and the bit-file.

From the results in Table I, we can observe that writing a combination of required VHDL design techniques in a single file takes more time, but if we want to edit for other parameters or design techniques, it will take an extra 15 minutes at later stages without the use of our tool flow. Using our portable tool flow, we can generate the synthesis results and the bit-file for all seven design parameters at the same time, so we can easily compare the results and choose the right implementation. Otherwise, we need to edit the design file each time and run the synthesis tool.

# *B.* Evaluating the portable VHDL design tool flow for multiple design files (H264 Video encoder design)

In this section, we evaluate our tool flow for the complete hardware H264 video encoder design, which consists of 15 different design blocks, as shown in Table II. Here, we added six design parameters in the design blocks. Using 6 different design parameters in the H264 encoder design, we are able to generate 8 different combinations, by selecting one design parameter each time or multiple design parameters in various combinations, which leads to different implementations and results. Using our tool flow here, we have the option of customisation by making parameter selections to a few design blocks.

Apart from portability options, we provide the automation option in running the complete synthesis steps. Using our tool flow, we can check the resource utilization for each design block. Our tool flow runs the synthesis step in parallel. A few more comparisons are tabulated in Table III.

|                                       | Number of design blocks | Number of design<br>parameters used | Design parameters used                                                                                                         | Number of possible<br>design<br>implementations | Customisation option<br>between different<br>design blocks |

|---------------------------------------|-------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------|

| Hardware H264<br>Video encoder design | 15                      | 6                                   | 1. Pipelined<br>2. Nonpipelined.<br>3. Less flip-flop design<br>4. More flip-flopdesign<br>5. Reduced logic<br>6. Normal logic | 8                                               | Yes                                                        |

TABLE II. EVALUATION OF HARDWARE VIDEO ENCODER H264 USING PORTABLE VHDL DESIGN TOOL FLOW

#### VI. CONCLUSION

In this paper, we proposed a way to combine the different possible VHDL design techniques and methods in a single VHDL design file. This can be evaluated into multiple (functionally equivalent) design files, that can be compared to allow the designer to choose between different implementation techniques, based on the achieved trade-off between FPGA resource utilisation and performance. In that way, by evaluating the same VHDL design file, the designer can estimate which design option is the better choice.

Additionally, we proposed a tool flow that allows the user to generate the design bit-files of all possible combinations automatically. This tool flow can be integrated into any other synthesis tool. Hence, it forms a pre-synthesis step, that provides the user with the flexibility of having multiple design TABLE III. COMPARISON OF PORTABLE VHDL DESIGN TOOL FLOW OVER USUAL TOOL COMMAND LANGUAGE (TCL) AUTOMATION

|                             | FPGA<br>architecture<br>independent | Parallel<br>implementation of<br>synthesis steps for<br>multiple boards | Need to change in<br>the design file for<br>other parameters | Synthesis report on same screen | Synthesis report for<br>each design file |

|-----------------------------|-------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------|------------------------------------------|

| Using Portable tool<br>flow | Yes                                 | Yes                                                                     | No                                                           | Yes                             | Yes                                      |

| Using normal automation TCL | No                                  | No                                                                      | Yes                                                          | No                              | No                                       |

options, but without having to redesign them, only to generate the new file, based on a set of parameters.

Using our tool flow, designers can easily redo the design exploration when the underlying FPGA architecture for the design changes. They do not have to delve into the VHDL source code for this. For the final design parameter choice, the tool can automatically generate the bitstream. Hence, this tool flow significantly enhances the portability of designs to new FPGA devices.

#### ACKNOWLEDGMENT

This work was supported by the Help Video! imec.icon research Project, funded by imec and the Flemish government (Agentschap innoveren and ondernemen).

#### REFERENCES

- [1] J. de Fine Licht, M. Blott, and T. Hoefler, "Designing scalable FPGA architectures using high-level synthesis," Proceedings of the 23rd ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, 2018, pp. 403–404. [Online]. Available: http://doi.acm.org/10.1145/3178487.3178527

- [2] K.Kuusilinna, Timo.Hmlinen, and Jukka.Saarinen, "Practical VHDL optimization for timing critical FPGA applications," Microprocessors and Microsystems, vol. 23, no. 8, pp. 459–469.

- [3] P. I. Necsulescu and V. Groza, "Automatic generation of VHDL hardware code from data flow graphs," 2011 6th IEEE International Symposium on Applied Computational Intelligence and Informatics (SACI), May 2011, pp. 523–528.

- [4] P. P. Chu, "Coding for efficiency, portability, and scalability," hardware design using VHDL, 2006, pp 50-100, ISSN:13: 978-0-471-72092-8.

- [5] Xilinx corporation "Xilinx product guide", 1.1, 2006, URL: https://bit.ly/2Gz2RO9/ [accessed: 2019-09-17].

- [6] T. Davidson, K. Bruneel, and D. Stroobandt, "Identifying opportunities for dynamic circuit specialization," 2012, workshop on Self-Awareness in Reconfigurable Computing Systems Proceedings, Oslo Norway, p-p 18-21. [Online]. Available: http://srcs12.doc.ic.ac.uk/docs/srcs\_proceedings.pdf

- [7] M. Arora, "The art of hardware architecture, design methods and techniques for digital circuits," Design Methods and Techniques for Digital Circuits, springer-Verlag New York, 2011, DOI:10.1007/978-1-4614-0397-5.

- [8] R. Jasinski, Effective Coding with VHDL: Principles and Best Practice. The MIT Press, 2016.

- [9] J. C. Baraza, J. Gracia, D. Gil, and P. J. Gil, "Improvement of fault injection techniques based on VHDL code modification," Tenth IEEE International High-Level Design Validation and Test Workshop, 2005., Nov 2005, pp. 19–26.

- [10] R. P. P. Singh, P. Kumar, and B. Singh, "Performance analysis of fast adders using VHDL," 2009 International Conference on Advances in Recent Technologies in Communication and Computing, Oct 2009, pp. 189–193.

- [11] Z. Zhang, Q. Yu, L. Njilla, and C. Kamhoua, "FPGA-oriented moving target defense against security threats from malicious FPGA tools," 2018 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), April 2018, pp. 163–166.

- [12] Z. Jia, B. Qi, L. Chen, H. Chen, and L. Ma, "Relative radiometric correction for remote sensing images based on VIVADO HLS," IET International Radar Conference 2015, Oct 2015, pp. 1–4.

- [13] V. S. Rosa, F. F. Daitx, E. Costa, and S. Bampi, "Design flow for the generation of optimized FIR filters," Dec 2009, pp. 1000–1003.

- [14] G. Donzellini and D. Ponta, "From gates to FPGA learning digital design with deeds," March 2013, pp. 41–48.

- [15] M. S. Sutaone and S. C. Badwaik, "Performance evaluation of VHDL coding techniques for optimized implementation of ieee 802.3 transmitter," Jan 2008, pp. 287–293.

- [16] Altera corporation, Altera product guide, 9.1, 2009, URL: http://bit.do/eJsnK/ [accessed: 2019-09-17].

- [17] Github link, URL: https://bit.ly/2Sh1kgU/.

- [18] Xilinx vivado URL: https://bit.ly/2AVvccx.

# **Implementation of an FPGA - Raspberry Pi SPI Connection**

Haissam Hajjar Department of Applied Business Computer, Faculty of Technology, Lebanese University Saîda, Lebanon haissamh@ul.edu.lb

Abstract— The use of Field Programmable Gate Arrays (FPGAs) requires low level programming. This makes it difficult to have a friendly user interface. The presented work explains FPGA techniques in detail. There are few works demonstrating an application integrating FPGA and ergonomic user-interface techniques. This article describes the connection of an FPGA to a Raspberry PI using a Serial Peripheral Interface (SPI) link. A Python SPI driver is developed on the Raspberry side. A Very High-Speed Integrated Circuit Hardware Description Language (VHDL) driver is developed on the FPGA side. A Web client-server application is developed to demonstrate the usage of SPI link and its integration with a standard Web application to control the FPGA inputs and outputs.

Keywords—SPI VHDL driver; VHDL; Raspberry PI; Altera Cyclone II; Python VHDL communication; Python-PHP socket communication.

#### I. INTRODUCTION

FPGAs are typically used in electronic circuits. Usually, they are programed in VHDL or Verilog [1]. This is well suited to stay at the hardware level but remains very poor and complex when developing a user-friendly humanmachine interface.

The VHDL implementation of SPI protocol is developed in some previous works [2][3]. However, these works focus their efforts on the electronic aspect by neglecting the application aspect.

The objective of this paper is to connect an FPGA to a Raspberry PI so that one side can use the FPGA for the electronic part, while the Raspberry PI can be used to develop a friendly user interface using common well-known techniques. The utilization of a Raspberry PI is taken to demonstrate a low-cost solution for this implementation.

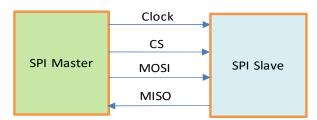

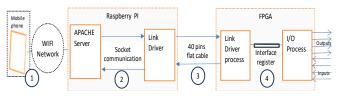

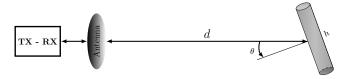

As the Raspberry runs under Linux operating system and the FPGA is programmed at an electronic level, we elected to use the SPI standard that does not need to use a common clock (see Figure 1). The communication is synchronized by a clock signal delivered by the SPI Master, independently of the internal clock frequency of each side.

On the programming language level, we choose to use Python for the Linux side (Raspberry) and VHDL for the FPGA side. So, the SPI driver can be integrated with the commonly used frameworks on the Linux side. Hussein Mourad Department of Applied Business Computer, Faculty of Technology, Lebanese University Saîda, Lebanon mourad\_hussein@hotmail.com

Figure 1. SPI Single Master – Single Slave signals - Chip Select (CS), Master Out Slave In (MOSI), Master In Slave Out (MISO)

This paper covers the following topics: Section I has provided an introduction. In Section II, we give a functional description of the implemented system. In Section III, we describe the hardware implementation and the materials used. In Section IV, we develop the SPI implementation on the Master level and the Slave level. In Section V, we present testing results of the SPI. In Section VI, we describe a high-level user interface developed to illustrate the SPI utilization. Finally, a conclusion is included in Section VII.

#### II. FUNCTIONAL DESCRIPTION

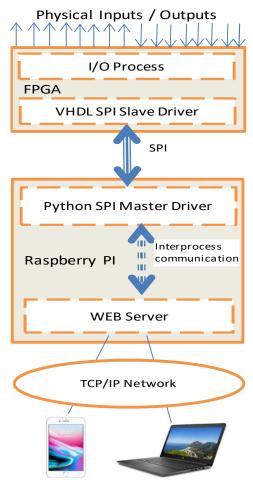

Figure 2 illustrates a functional representation of the whole system:

#### A. Raspberry PI

A Raspberry PI 3 [4] functions as Master of the SPI link. The Raspberry PI is equipped with a General Purpose Input/Output (GPIO). The SPI was implemented using 4 lines of this GPIO. A Python implementation of SPI Master is utilized. An Apache Web server is implemented inside the Raspberry to allow implementation of ergonomic and easy to use interface for testing and demonstration purposes. A SPI Master driver is developed using Python language and libraries. As the system must work efficiently with regards to real time response time, two independent processes were implemented within the Raspberry PI system:

- To handle the user requests: an Apache Web server is implemented using PHP scripting for the Web server side.

- To handle the SPI link during the communication with the FPGA. This driver is written using Python.

• The communication between these two processes is executed using TCP/IP socket communication.

Figure 2. Functional representation

### B. FPGA

An 'Altera DE2' Development and Education Board' [5] is used to implement the FPGA part. This board is built on a Cyclone II EP2C35F672C6 FPGA working up to 50 MHz clock frequency. This board has a 2 lines/16-character LCD display, a set of 18 toggle switches for digital inputs, a set of 4 pushbuttons, a set of 18 red led for digital outputs and 2 forty lines extension headers for external connection. The SPI is implemented using one of these extension headers.

To illustrate the successful operation of the SPI link, we devise three functional usages:

- Send order, starting from the user interface, to drive the 18 FPGA board digital outputs

- Receive the status of the 18 lines of digital input to display on the user screen.

- Send 32 bytes, entered on the user screen, in order to be displayed on the FPGA LCD 2 lines display.

Compared to OSI communication layer, we can consider the SPI drivers as the physical layer and these functional usages as a link layer. So, this can be extended to implement other functional types of messages exchanged between the FPGA and the Raspberry.

**TCP/IP network:** The Raspberry PI has an 802.11 Wi-Fi 2.4 GHz interface. This interface is used to allow the connection of a Web-based client using a standard browser. A Web-based user interface is developed to allow the usage of the previously mentioned illustration function for the use of the SPI connection.

#### III. PHYSICAL IMPLEMENTATION

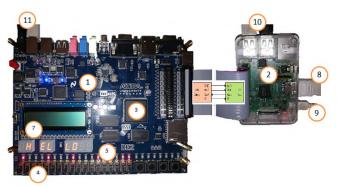

Figure 3 represents the physical implementation:

Figure 3. Physical implementation

- 1. DE2 Development and Education Board: we use this board for the FPGA implementation part. For detailed documentation, refer to the Intel official documentation [5]

- Raspberry Pi 3 board [3]: this board is equipped with 1 GB Ram, processor Cortex-A53 (ARMv8) 64-bit SoC @ 1.4GHz.

- 3. Cyclone® II 2C35 FPGA in a 672-pin package, working at 50 MHz

- 4. 18 switches used as digital inputs

- 5. 18 LEDs used as digital outputs

- 6. 40 pins flat cable used as connector between the Raspberry GPIO and the extension header of the DE2 board. This cable is used to implements the SPI connection between the Raspberry PI and the Altera DE2 FPGA evaluation board.

- 7. 2x16 LCD and eight 7 segment digital display

- 8. HDMI connector for Raspberry PI

- 9. Power supply for Raspberry PI

- 10. Mouse and keyboard USB connectors

- 11. Power Supply and Programmer connection

#### IV. SPI IMPLEMENTATION

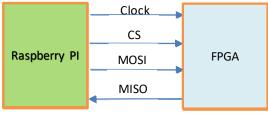

The implemented system is represented in Figure 4. A single Master with single Slave scenario is shown in the following paragraphs.

#### A. Physical interface

Figure 4 presents the SPI signals. The Raspberry PI is the master and the FPGA is the slave. A configuration of one Master/one Slave is implemented:

Figure 4. SPI implementation

- Clock: the clock is generated by the Master. This signal drives the communication in both directions.

- CS (Chip Select) high when the FPGA is not selected: No communication; low when selected.

- MOSI: Master Out Slave In: data transferred from the Master to the Slave.

- MISO: Master In Slave Out: data transmitted from the Slave to the Master.

#### B. Implementation principle

The communication is driven by the Master. The first byte determines the type of communication. To illustrate the usage of the drivers, three types of messages were implemented:

- Send Memory: The Master sends to the Slave 32 bytes of data for displaying on the LCD.

- Send Outputs: The Master sends to the Slave the order to set its digital outputs ON or OFF

- Receive Inputs: The Slave sends to the Master the status of its digital inputs.

### C. Master Driver

This driver is based on the RPI.GPIO Python library [9]. After initialization, two functions are available for an upper level usage:

Sendbyte: send a byte from Master to Slave.

Receivebyte: receive a byte from Slave to Master.

To send a bit, MOSI is set, and then a Clock is generated (SCLK from Low to High).

To receive a bit, a Clock rising is generated, and then the MISO line level is read.

SPI Initialization (Figure 5): the GPIO of the Raspberry includes 2 SPI lines. We had trouble driving these lines with the standard Raspberry library. We opted to drive the SPI signals directly through our program. This allowed us to control the CS and Clock lines easily and to reach the maximum possible communication speed with a Python driver.

```

import RPi.GPIO as GPIO

# Line definition

MOSI = 5

MISO = 10

SCLK = 15

CEO = 7

#

# SPI line initialization

def initspi():

GPIO.setmode(GPIO.BOARD)

GPIO.setwarnings(False)

GPIO.setup(MOSI, GPIO.OUT)

GPIO.setup(MISO, GPIO.IN)

GPIO.setup(SCLK, GPIO.OUT)

GPIO.setup(CE0, GPIO.OUT)

```

Figure 5. Master driver - SPI initialization

Send byte (Figure 6): The transmission of a byte starts with the change of the signal CS (CS low). This will initiate the reception process on the VHDL side. The MOSI level is set according to the bits to be sent and a clock signal is generated. After transmission of the 8 bits, this CS signal returns to the high level.

```

def sendbyte(cc):

c=ord(cc)

# select slave

GPIO.output(CE0, GPIO.LOW)

bitsx = [0, 0, 0, 0, 0, 0, 0, 0]

# determine bits 0/1

for x in range(8):

bitsx[7-x] = int(c \% 2)

c = int((c - bitsx[7-x])/2)

# set Mosi signal level

for x in range(8):

if (bitsx[x]>0):

GPIO.output (MOSI,

GPIO.HIGH)

else:

GPIO.output (MOSI, GPIO.LOW)

# clock

GPIO.output(SCLK, GPIO.LOW)

GPIO.output(SCLK, GPIO.HIGH)

# end of byte transmission

GPIO.output(CE0, GPIO.HIGH)

GPIO.output(SCLK, GPIO.LOW)

GPIO.output(SCLK, GPIO.HIGH)

```

Figure 6. Master driver - Send byte

Receive byte (Figure 7): The reception of a byte starts with the change of the signal CS (CS low). This will initiate the transmission process on the VHDL side. The MISO level is read according to the bits received each clock signal generated. After reception of the 8 bits, this CS signal returns to the high level.

```

def receivebyte():

GPIO.output(SCLK, GPIO.LOW)

# select slave

GPIO.output(CEO, GPIO.LOW)

out = 0b0

# read 8 bits on MISO

for x in range(8):

GPIO.output(SCLK, GPIO.LOW)

GPIO.output(SCLK, GPIO.HIGH)

out = out*2

if GPIO.input(MISO):

out = out + 1

GPIO.output(CEO, GPIO.HIGH)

return out

```

Figure 7. Master driver - Receivebyte

#### D. Slave Driver

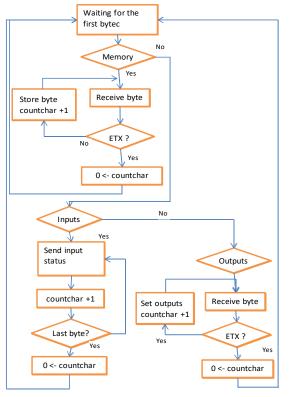

Figure 8 presents the process handling the communication on the FPGA.

Figure 8. Master driver - Receivebyte

The process is normally in a waiting state. It is activated by the CS signal. When the CS is down, the FPGA reads the bits set on MOSI signal on rising edge of Clock signal.

```

process (SCK,CS,reset)

begin

if (CS = '1' and octet=MasterToSlaveMemory) then

countbit <= 0; countchar <= 0;

direction <= RECEIVE_MEMORY;

elsif (CS = '1' and octet=MasterToSlaveOutput) then

countbit <= 0; countchar <= 0;

direction <= RECEIVE_OUTPUTS;

elsif (CS = '1' and octet=SlaveToMaster) then

countbit <= 0; countchar <= 0;

direction <= SEND_INPUTS;

elsif .....</pre>

```

Figure 9. Slave driver - Message type detection

When the first byte is received, it is tested. Three cases are considered:

• 'Send Memory': the FPGA continues the reception of the following bytes. The received bytes are stored in an internal memory indexed by a reception counter. This will end when an EOT is received.

```

-- Receive memory

if (rising edge(SCK) and CS='0'

and direction=RECEIVE MEMORY) then

octet <= octet(size-2 downto 0) & mosi;

countbit <= countbit+1;</pre>

if (countbit=7) then

memory(countchar) <= octet(size-2 downto 0) &

mosi;

if memory(countchar) = EOT then

countchar \leq 0;

else

countchar \leq countchar+1;

end if;

countbit \leq 0;

end if;

end if;

```

Figure 10. Slave driver - Receive memory

• 'Send outputs': the FPGA continues the reception of data. The outputs are set/unset according to the received data.

| Receive Outputs                                          |

|----------------------------------------------------------|

| if (rising edge(SCK) and CS='0' and                      |

| direction=RECEIVE OUTPUTS) then                          |

| Receive 3 bytes [18 bits only valid] for digital outputs |

| outputs(countchar)(7-countbit) <= mosi;                  |

| countbit <= countbit+1;                                  |

| if (countbit=7) then                                     |

| if memory(countchar) = EOT then                          |

| countchar <= 0;                                          |

| else                                                     |

| countchar $\leq$ countchar+1;                            |

| end if;                                                  |

| countbit <= 0;                                           |

| end if; end if;                                          |

Figure 11. Slave driver - Receive outputs

• 'Receive inputs': the FPGA sends the status of its digital inputs [3 bytes for 18 inputs] using the MISO line. An EOT is sent to inform the Master that the end of sending is reached.

Figure 12. Slave driver - Request to send inputs

#### V. TESTING AND RESULTS

We present three tests executed to validate communication using this implementation of SPI.

#### A. Setting outputs

Send order from the Master (Raspberry PI) to the Slave (Altera FPGA DE2 board) to set/unset its digital outputs: 'Oxxx': Message of 4 bytes. The first byte represents the type of message; the following bytes represent the required outputs status.

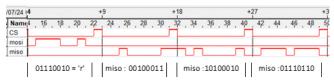

Figure 13 shows the signals observed on the SPI lines. The message sent from the Master: the first byte represents the ASCII representation of the character O (01101111) used as identifier for this message. As described in Section IV, the following 3 bytes represent the value to be set on the digital outputs. The following 3 bytes represent the requested status of FPGA 18 lines output.

Figure 13. Signals on the SPI lines for sending outputs

Each byte starts when the CS comes down and is sent when the CS goes up again. Figure 14 shows the LEDs corresponding to the signal shown in Figure 13. The LED is on when '1' is received and is off when '0' is received.

Figure 14: Led status on the FPGA board

#### B. Read inputs

Send order from the Master (Raspberry PI) to the Slave (Altera FPGA DE2 board) 'r': This message asks the FPGA to send back to the Raspberry the status of its digital inputs. The Raspberry (Master) must continue to generate the clock. The next bytes are sent by the FPGA (Slave) to the master over the MISO line. As we have 18 inputs, three bytes are used for this function.

Figure 15 shows the SPI signals: the clock is always given by the Master. The Master sends the first 'r' byte (01110100) over the MOSI signal. Then, the Slave sends back three bytes.

Figure 15: Signals on the SPI lines for read inputs outputs

Figure 16 shows the input switches generating the signals shown in Figure 15.

Figure 16. Input switch corresponding to Schema 6 signals

#### C. Performance

The performance of this link depends on the SPI Master. For the Raspberry III utilized, the speed of 100kb/s was reached.

#### VI. APPLICATION TESTING

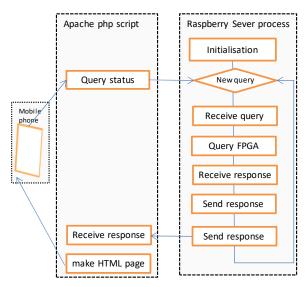

An application is developed to show a concreate utilization of this work. Figure 17 shows a functional representation of this realization.

Figure 17. Signals on the SPI lines for sending outputs

The implementation inside the Raspberry PI is performed using two processes: an Apache server and the SPI link driver. This is done for real time constraints. The communication between these two processes is executed using client/server socket communication. The Apache side is developed in PHP and the SPI link driver side is developed in Python. Figure 18 presents the principle of this communication. Figure 19 shows the user-interface on a smartphone screen using a standard Web browser.

Figure 18. Client/server communication in Raspberry PI

The number of inputs and outputs are reduced to 8 to have an ergonomic user-interface on smartphones. The status of the digital inputs of the FPGA is reported on the user screen. The digital outputs of the FPGA are set according to the radio-button.

Figure 19. User interface print screen

#### VII. CONCLUSION

In this work, FPGA-Raspberry Pi communication is developed using the SPI protocol. A high level application is developed using this link. This demonstrates a solution that works by using a low level technique (VHDL) on the FPGA side and using a high level technique on the user interface side.

We have limited the application to digital inputs / outputs. The work can be extended to other functions of the FPGA. This opens the possibility of modifying the behavior of an FPGA dynamically. The job can also be completed in the sense of increasing the transmission speed, which is somehow proportional to the Master's clock frequency.

#### References

- [1] https://circuitdigest.com/tutorial/what-is-fpgaintroduction-and-programming-tools (9/2019)

- [2] N.Q.B.M. Noor and A. Saparon, "FPGA implementation of high speed serial peripheral interface for motion controller," in Proc. 2012 IEEE Symposium on Industrial Electronics and Applications (ISIEA), pp.78-83, Sept. 2012.

- [3] Raspberi Pi official site: https://www.raspberrypi.org/ documentation/hardware/raspberrypi/spi/ (1/2019)

- [4] Rapberry Pi 3 board Official documentation https://www.raspberrypi.org/products/raspberry-pi-3model-b-plus/ (1/2019)

- [5] Altera DE2-115 Development and Education Board https://www.intel.com/content/www/us/en/programmab le/solutions/partners/partner-profile/terasic-inc-/board/altera-de2-115-development-and-educationboard.html

- [6] Python documentation, https://www.python.org/ (1/2019)

- [7] https://www.php.net/manual/fr/ (1/2019)

- [8] Quartus II Handbook: http://www.altera.com/literature/hb/qts/quartusii\_handb ook.pdf (4/2019)

- [9] GPIO Raspberry installation and usage : https://www.raspberrypi-spy.co.uk/2012/05/install-rpigpio-python-library/ (6/2019)

- [10] SPI Tutorial COREIS https://www.corelis.com/ education/tutorials/spi-tutorial/ (5/2019)

# Accelerating FPGA-Placement With a Gradient Descent Based Algorithm

Timm Bostelmann, Tobias Thiemann and Sergei Sawitzki

FH Wedel (University of Applied Sciences) Wedel, Germany Email: {bos, inf103917, saw}@fh-wedel.de

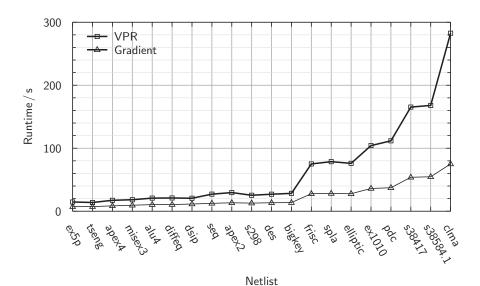

Abstract—Programmable circuits and, nowadays, especially Field-Programmable Gate Arrays (FPGAs) are widely applied in computationally demanding signal processing applications. Considering modern, agile hardware/software codesign approaches, an Electronic Design Automation (EDA) process not only needs to deliver high quality results, but also has to be swift because software compilation is already distinctly faster. Slow EDA tools can in fact act as a kind of show-stopper for an agile development process. One of the major problems in EDA is the placement of the technology-mapped netlist to the target architecture. In this work, a method to reduce the runtime of the netlist placement for FPGAs is evaluated. The approach is a variation of analytical placement, with the distinction that a gradient descent is used for the optimization of the placement. This work is based on previous publications of the authors, in which a placement algorithm using self-organizing maps is introduced and optimized. In comparison, the gradient placement approach is shown to be up to 3.8 times faster than the simulated annealing based reference with about the same quality regarding the bounding-box and routingresource costs.

#### Keywords-EDA; FPGA; placement; gradient descent.

#### I. INTRODUCTION

The ever-growing complexity of Field-Programmable Gate Arrays (FPGAs) has a high impact on the performance of Electronic Design Automation (EDA) tools. A complete compilation from a hardware description language to a bitstream can take several hours. One step highly affected by the vast size of netlists is the NP-equivalent placement process. It consists of selecting a resource cell (position) on the FPGA for every cell of the applications netlist. In previous publications of the authors, a placement algorithm for FPGAs based on a self-organizing map [1] was presented [2] and optimized [3]. With that approach, placements of high quality were produced. However, it was relatively slow for large netlists, even when accelerated using a Graphics Processing Unit (GPU) [4]. Therefore, in this work, a faster approach for netlist placement based on a gradient descent is presented as an updated version of the authors' previous work [4].

Due to the complexity of the netlist placement problem, many current algorithms work in an iterative manner. A well known example is simulated annealing [5], which starts with a random initial placement and swaps blocks stepwise. The result of every step is evaluated by a cost function. A step is always accepted, if it reduces the cost. If it increases the cost, it is accepted with a probability that declines with time (cooling down). An annealing schedule determines the gradual decrease of the temperature, where a low temperature means a low acceptance rate and a high temperature means a high acceptance rate. Generally, the temperature is described by an exponentially falling function like

$$T_n = \alpha^n \cdot T_0, \tag{1}$$

where typically  $0.7 \le \alpha \le 0.95$ . However, there has been a lot of research on the optimization of the annealing schedule like in [6][7]. As a result, there are many variations available for any related problem.

Analytical placement is a different approach, where the problem is described as a system of equations. By solving this system of equations, the optimal position for every element can be derived. However, solving such large equation systems takes much time. Therefore, Vansteenkiste et al. [8] have introduced a method to approximate the solution of the equation system by the steepest gradient descent. This approach is shown to be two times faster than a conventional analytical placement on average, without any penalties in quality.

In this work, a simplified implementation of the steepest gradient descent placement is described and benchmarked extensively. It is not compared to other analytical placement methods. Instead, the established implementation of the simulated annealing approach of the Versatile Place and Route (VPR) tool [9] for FPGAs is used as reference.

In Section II, the problem of netlist placement for FPGAs is introduced and the principle of netlist placement with a gradient descent is described. In Section III, the proposed algorithm is described including some details of its implementation. In Section IV, the results of the proposed algorithm are presented. As representation for real world applications, a set of twenty Microelectronics Center of North Carolina (MCNC) benchmarks [10] is used. Finally, in Section V, the results of this work are summarized and a prospect to further work is given.

#### II. BACKGROUND

This section is separated into two parts. First, the problem of netlist placement for FPGAs is introduced. Second, the general idea of using a gradient descent for the placement of netlists for FPGAs is described.

#### A. Netlist Placement for FPGAs

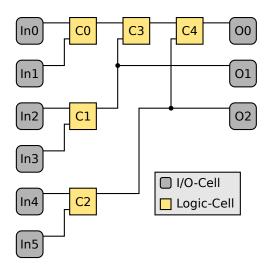

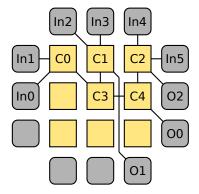

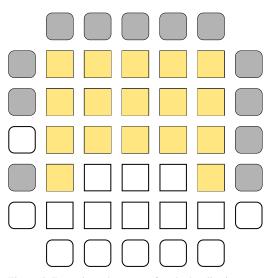

The problem of netlist placement for FPGAs can be roughly described as selecting a resource cell (a position) on the target FPGA for every cell of the given netlist. In Figure 1, an exemplary graph of a netlist is defined. An exemplary

Figure 1. An exemplary graph of a netlist consisting of input-, output-, and logic-cells.

Figure 2. A valid placement for the graph in Figure 1 on a simple island-style FPGA architecture.

placement for this netlist is presented in Figure 2. The positions must be chosen in a way that:

- 1) Every cell of the netlist is assigned to a resource cell of the fitting type (e.g., Input/Output or Logic).

- 2) No resource cell is occupied by more than one cell of the netlist.

- 3) The cells are arranged in a way that allows the best possible routing.

The first two rules are necessary constraints. A placement that is failing at least one of these two constraints is illegal and, therefore, unusable. The third rule is a quality constraint, which is typically described by a cost function. The goal of a placement algorithm is to optimize the placement regarding this function without violating one of the necessary constraints. Usually, the length of the critical path and the routability are covered by the cost function.

#### B. Netlist Placement With a Gradient Descent

The netlist placement with a gradient descent is done by iteratively optimizing the positions of all elements of the netlist in the direction of the steepest gradient descent. During this process, the nodes are not bound to the grid of the FPGA architecture. Instead, they are positioned in a continuous space. To generate a valid placement – without overlapping and under consideration of the FPGA's architecture – in this approach, a cycle of optimization and legalization is used. This procedure is customary for analytical placement methods for FPGAs, like Gort and Anderson have introduced in [11]. A different approach would be to generate only valid placements by exclusively moving the nodes on the architectural grid of the FPGA.

#### III. IMPLEMENTATION

#### A. Gradient Calculation

At the beginning of every optimization step, the boundingbox size of every net in the netlist is determined. This is a necessary preparation for the cost-function, which is described later in this section. To determine the size of a net, all nodes with a connection to the net are determined. For all these nodes, the minimum and maximum of the horizontal positions  $(X_i)$  and the vertical positions  $(Y_i)$  are determined and stored for the calculation of the gradient. Additionally, the sum of all sizes in X and Y direction is calculated, as a metric for the global quality of the current placement.

The goal of every optimization step is to move the nodes in a direction that leads to a reduction of the bounding-box size of the containing net. A cost-function is necessary to determine the influence of every node on the size of the corresponding net. The gradient of this cost-function can then be used to determine the direction of the movement of each node. All nodes of the netlist are moved towards the steepest gradient descent to reduce the global cost.

An intuitive approach would be to use the sum of the bounding-box sizes of all nets as cost-function. However, with this metric, only the outermost nodes would be moved and even nodes that are very near to the bounding-box would be ignored. Furthermore, the min and max functions contained in the metric can not be derived to calculate the gradient.

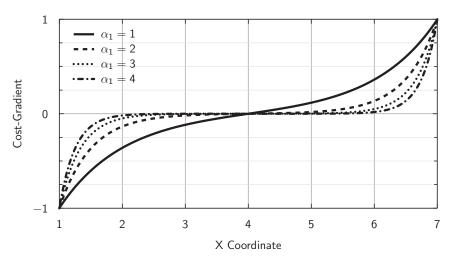

To solve these issues, an exponential function over the distance between the position of the node and the boundingbox of the net is chosen as basis of the cost-function. The cost-function for a node with the index k is

$$C_{k} = \alpha_{2} \cdot \sum_{n \in N_{k}} \left( e^{\alpha_{1} \cdot (x_{k} - \max_{x}(n))} + e^{\alpha_{1} \cdot (\min_{x}(n) - x_{k})} + e^{\alpha_{1} \cdot (y_{k} - \max_{y}(n))} + e^{\alpha_{1} \cdot (\min_{y}(n) - y_{k})} \right),$$

(2)

where  $x_k$  and  $y_k$  describe the X and Y coordinates of the current node,  $N_k$  describes the set of all nets that contain the node and min<sub>x</sub>, max<sub>x</sub>, min<sub>y</sub> and max<sub>y</sub> are the minimal and maximal coordinates of the current net (i.e., the boundingbox).  $\alpha_1$  and  $\alpha_2$  are parameters for the cost-function, which allow to influence the behavior of the function. With  $\alpha_1$ , it can be determined how large the distance between the node and the bounding-box must be to reduce its influence in the cost-function. The influence of  $\alpha_1$  on the gradient is shown in Figure 3 for the X coordinate of a node, assuming a net with the boundaries min<sub>x</sub> = 1 and max<sub>x</sub> = 7. With  $\alpha_2$ , the cost can be increased or reduced to influence the steepness of the gradient.

Based on (2), the gradients for the X and Y coordinates

Figure 3. Exemplary plot of possible gradients for the X coordinate of a node, assuming a net with the boundaries  $\min_{x} = 1$  and  $\max_{x} = 7$ .

Figure 4. Exemplary placement before the legalization step.

can be calculated as

$$\frac{\partial C_k}{\partial x_k} = \alpha_2 \cdot \sum_{n \in N_k} \left( e^{\alpha_1 \cdot (x_k - \max_x(n))} - e^{\alpha_1 \cdot (\min_x(n) - x_k)} \right), \quad (3)$$

$$\frac{\partial C_k}{\partial y_k} = \alpha_2 \cdot \sum_{n \in N_k} \left( e^{\alpha_1 \cdot \left( y_k - \max_y(n) \right)} - e^{\alpha_1 \cdot \left( \min_y(n) - y_k \right)} \right).$$

(4)

As a result, the coordinates of nodes that are near the bounding-box of their containing net have a gradient of  $\pm \alpha_2$ , where the coordinates of nodes with a larger distance to the bounding-box have a much lower gradient, as shown in Figure 3. Consequentially, nodes with a larger gradient value must be moved further to improve the placement optimally.

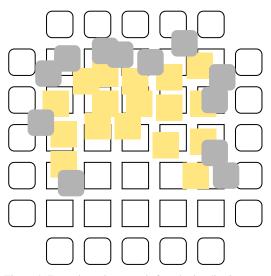

#### B. Legalization

During the optimization step, the nodes can take any position. Thereby, illegal placements are produced, due to overlapping of nodes, as well as violation of the architectural grid of the FPGA. Therefore, the optimized placement must be legalized in a separate step. This is done by finding the

Figure 5. Exemplary placement after the legalization step.

nearest valid position for every node, as depicted in Figure 4 (before the legalization) and Figure 5 (after the legalization).

The algorithm for the legalization is inspired by the work of Gort and Anderson [11]. The basic idea of that approach is to find regions that contain more nodes than the corresponding region of the FPGA provides. Then, those regions are gradually expanded. When two regions overlap, they are merged. This is done until the regions are large enough to place all contained nodes to a proper resource cell of the FPGA. In the next step, the regions are split recursively and the nodes are assigned to the new sections by their position. This is repeated until a region contains no more nodes, or only one node. In the latter case, the position of the single remaining node is set to the position of its containing region.

In this work, the search for regions that contain more nodes than the corresponding region of the FPGA provides and the following expansion and merge phases are skipped. Instead, all nodes are assigned to one large region from the start and the phase of recursive splitting starts directly. By this measure, the computational effort for the legalization is reduced significantly without a dramatic impact on the global quality. This is because – especially when a large amount of the available resources is used – the result of the expansion phase is containing usually very few large regions or often only one large region anyway.

#### C. Optimization

For the optimization, the algorithm Adam – which was introduced by Kingma and Ba in [12] – is used. The used update rules are:

| $g_t = \Delta \phi_t$                                                                    | Gradient of the variable  |

|------------------------------------------------------------------------------------------|---------------------------|

| $m_t = \beta_1 \cdot m_{t-1} + (1 - \beta_1) \cdot g_t$                                  | Running average force one |

| $v_t = \beta_2 \cdot v_{t-1} + (1 - \beta_2) \cdot g_t^2$                                | Running average force two |

| $\hat{m}_t = m_t / \left(1 - \beta_1^t\right)$                                           | Bias corrected force one  |

| $\hat{v}_t = v_t / \left(1 - \beta_2^t\right)$                                           | Bias corrected force two  |

| $\phi_t = \phi_{t-1} - S_a \cdot \hat{m}_t / \left( \sqrt{\hat{v}_t} + \epsilon \right)$ | Update of the variable    |

The constants  $\beta_1$  and  $\beta_2$  define how fast the averages of the first and second forces change. In this work, the constants were defined as  $\beta_1 = 0.96$  and  $\beta_2 = 0.998$ . The variable  $S_a$  defines the learning rate or, more specifically, the step-width. It starts at  $S_a = 1.5$ , but changes over time (i.e., in the different phases of the placement).

#### D. Placement Phases

The previously described steps are executed for every iteration. The placement process is separated into five phases, with different parameters. Each phase consists of a given number of iterations. The number of iterations per phase was determined empirically and is fixed (i.e., independent of the size of the design). The phases are:

Presorting (5000 iterations) In this phase, all nodes are moved with a high step width in the general direction of their final position.

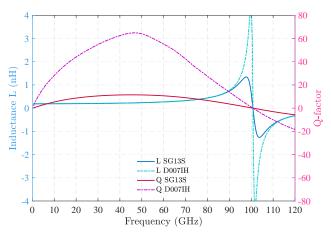

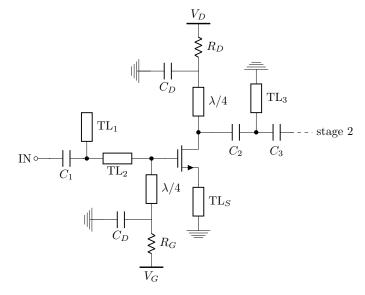

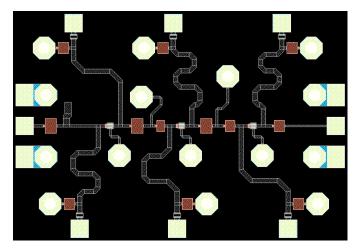

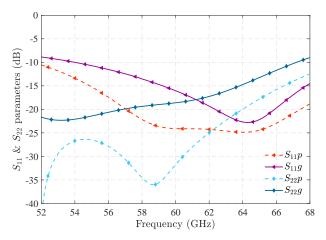

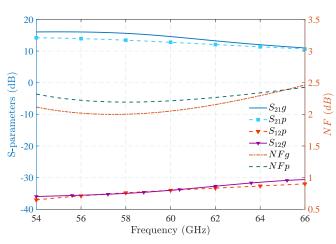

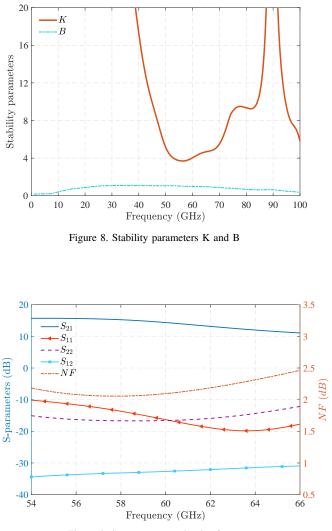

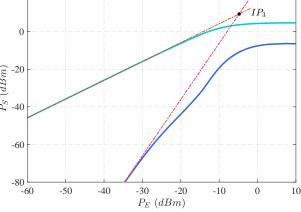

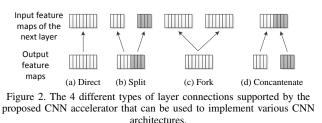

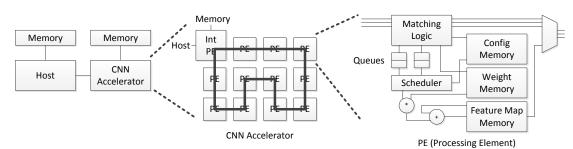

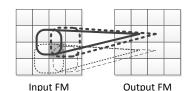

Grid placement (1000 iterations)