# **DEPEND 2016**

The Ninth International Conference on Dependability

ISBN: 978-1-61208-492-3

July 24 - 28, 2016

Nice, France

## **DEPEND 2016 Editors**

Elena Troubitsyna, Abo Akademi University, Finland

Pascal Lorenz, University of Haute Alsace, France

## **DEPEND 2016**

## Forward

The Ninth International Conference on Dependability (DEPEND 2016), held between July 24-28, 2016 in Nice, France, provided a forum for detailed exchange of ideas, techniques, and experiences with the goal of understanding the academia and the industry trends related to the new challenges in dependability on critical and complex information systems.

With large scale and complex systems, their parts expose different static and dynamic features that interact with each others; some systems are more stabile than others, some are more scalable, while others exhibit accurate feedback loops, or are more reliable or fault-tolerant.

Inter-system dependability and intra-system feature dependability require more attention from both theoretical and practical aspects, such as a more formal specification of operational and non-operational requirements, specification of synchronization mechanisms, or dependency exception handing.

We take here the opportunity to warmly thank all the members of the DEPEND 2016 technical program committee, as well as the reviewers. We also kindly thank all the authors that dedicated much of their time and effort to contribute to DEPEND 2016.

We also gratefully thank the members of the DEPEND 2016 organizing committee for their help in handling the logistics and for their work that made this professional meeting a success.

We hope DEPEND 2016 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in the area of dependability. We also hope that Nice, France provided a pleasant environment during the conference and everyone saved some time enjoy the beautiful French Riviera.

## **DEPEND 2016 Advisory Committee**

Sergio Pozo Hidalgo, University of Seville, Spain Manuel Gil Perez, University of Murcia, Spain Vincenzo De Florio, MOSAIC/Universiteit Antwerpen & MOSAIC/iMinds, Belgium

## **DEPEND 2016 Industry Liaison Chairs**

Piyi Yang, Wonders Information Co., Ltd., China Timothy Tsai, Hitachi Global Storage Technologies, USA

## **DEPEND 2016 Research/Industry Chair**

Michiaki Tatsubori, IBM Research Tokyo, Japan

## **DEPEND 2016 Special Area Chairs**

Cross-layers dependability Szu-Chi Wang, National Ilan University, Taiwan Big Data and dependability Cesario Di Sarno, University of Naples Parthenope, Italy Empirical assessments Marcello Cinque, University of Naples Federico II, Italy Security and Trust Syed Naqvi, Birmingham City University, United Kingdom

## **DEPEND 2016**

## Committee

## **DEPEND Advisory Committee**

Sergio Pozo Hidalgo, University of Seville, Spain Manuel Gil Perez, University of Murcia, Spain Vincenzo De Florio, MOSAIC/Universiteit Antwerpen & MOSAIC/iMinds, Belgium

## **DEPEND 2016 Industry Liaison Chairs**

Piyi Yang, Wonders Information Co., Ltd., China Timothy Tsai, Hitachi Global Storage Technologies, USA

## **DEPEND 2016 Research/Industry Chair**

Michiaki Tatsubori, IBM Research Tokyo, Japan

## **DEPEND 2016 Special Area Chairs**

## **Cross-layers dependability**

Szu-Chi Wang, National Ilan University, Taiwan

## **Big Data and dependability**

Cesario Di Sarno, University of Naples Parthenope, Italy

## **Empirical assessments**

Marcello Cinque, University of Naples Federico II, Italy

Security and Trust Syed Naqvi, Birmingham City University, United Kingdom

## **DEPEND 2016 Technical Program Committee**

Habtamu Abie, Norwegian Computing Centre, Norway Don Adjeroh, West Virginia University, USA Muhammad Afzaal, Lahore Leads University, Pakistan Joxe Inaxio Aizpurua Unanue, University of Strathclyde, UK Eduardo Alchieri, University of Brasília, Brazil Murali Annavaram, University of Southern California, USA Luciana Arantes, Université Pierre et Marie Curie (Paris 6), France Afonso Araújo Neto, University of Coimbra, Portugal José Enrique Armendáriz-Iñigo, Universidad Pública de Navarra, Spain Radu F. Babiceanu, Embry-Riddle Aeronautical University, USA Ian Bayley, Oxford Brookes University, U.K. Siegfried Benkner, University of Vienna, Austria Jorge Bernal Bernabé, University of Murcia, Spain James Brandt, Sandia National Laboratories, U.S.A. Andrey Brito, Universidade Federal de Campina Grande, Brazil Lasaro Camargos, Federal University of Uberlândia, Brazil Juan Carlos Ruiz, Universidad Politécnica de Valencia, Spain Antonio Casimiro Costa, University of Lisbon, Portugal Andrea Ceccarelli, University of Firenze, Italy Sudip Chakraborty, Valdosta State University, USA Binbin Chen, Advanced Digital Sciences Center, Singapore Albert M. K. Cheng, University of Houston, USA Marcello Cinque, University of Naples Federico II, Italy Peter Clarke, Florida International University, U.S.A. Luigi Coppolino, Università degli Studi di Napoli "Parthenope", Italy Domenico Cotroneo, Università di Napoli Federico II, Italy David de Andrés Martínez, Universitat Politècnica de València, Spain Rubén de Juan-Marín, Instituto Tecnológico de Informática, Spain Vincenzo De Florio, University of Antwerp, Belgium & IBBT, Belgium Raffaele Della Corte, "Federico II" University of Naples, Italy Ewen Denney, SGT/NASA Ames, U.S.A. Catello Di Martino, University of Illinois at Urbana-Champaign, U.S.A. Cesario Di Sarno, University of Naples Parthenope, Italy Tadashi Dohi, Hiroshima University, Japan Nicola Dragoni, Technical University of Denmark - Lyngby, Denmark Diana El Rabih, Université Paris 12, France Cain Evans, Birmingham City University, UK Camille Fayollas, Université Toulouse, France Francesco Flammini, Ansaldo STS, Italy Franco Frattolillo, University of Sannio, Italy Gregory Frazier, Apogee Research, U.S.A. Jicheng Fu, University of Central Oklahoma, U.S.A. Cristina Gacek, City University London, United Kingdom Joaquin Gracia Moran, Institute ITACA - Universitat Politecnica de Valencia, Spain Marisol García Valls, University Carlos III de Madrid, Spain Alessia Garofalo, COSIRE Group, Aversa, Italy Ann Gentile, Sandia National Laboratories, U.S.A. Manuel Gil Perez, University of Murcia, Spain Michael Goldsmith, University of Oxford, UK Patrick John Graydon, NASA, USA Michael Grottke, University of Erlangen-Nuremberg, Germany Nils Gruschka, University of Applied Science - Kiel, Germany Ibrahim Habli, University of York, U.K. Houcine Hassan, Universitat Politecnica de Valencia, Spain Bjarne E. Helvik, The Norwegian University of Science and Technology (NTNU) - Trondheim, Norway Luke Herbert, Technical University of Denmark, Denmark Pao-Ann Hsiung, National Chung Cheng University, Taiwan Jiankun Hu, Australian Defence Force Academy - Canberra, Australia

Neminath Hubballi, Infosys Lab Bangalore, India Bukhary Ikhwan Ismail, MIMOS Berhad, Malaysia Ravishankar K. Iyer, University of Illinois at Urbana-Champaign, U.S.A. Arshad Jhumka, University of Warwick - Coventry, UK Shouling Ji, Georgia Institute of Technology, USA Zhanpeng Jin, State University of New York at Binghamton, U.S.A. Yoshiaki Kakuda, Hiroshima City University, Japan Zbigniew Kalbarczyk, University of Illinois at Urbana-Champaign, U.S.A. Hui Kang, Stony Brook University, USA Aleksandra Karimaa, Turku University/TUCS and Teleste Corporation, Finland Sokratis K. Katsikas, Center for Cyber and Information Security - Gjøvik University College, Norway Dong-Seong Kim, University of Canterbury, New Zealand Ezzat Kirmani, St. Cloud State University, USA Seah Boon Keong, MIMOS Berhad, Malaysia Kenji Kono, Keio University, Japan Israel Koren, University of Massachusetts - Amherst, USA Mani Krishna, University of Massachusetts - Amherst, USA Mikel Larrea, University of the Basque Country UPV/EHU, Spain Inhwan Lee, Hanyang University - Seoul, Korea Matthew Leeke, University of Warwick, UK Jane W. S. Liu, Academia Sinica, Taiwan Yun Liu, Boeing Company, USA Xuanwen Luo, Sandvik Mining, USA Miroslaw Malek, Humboldt-Universitaet zu Berlin, Germany Amel Mammar, Mines Telecom/ Telecom SudParis, France Antonio Mana Gomez, University of Malaga, Spain Mohammad Mannan, Concordia University, Canada Gregorio Martinez, University of Murcia, Spain Célia Martinie, Université Toulouse 3, France Rivalino Matias Jr., Federal University of Uberlandia, Brazil Yutaka Matsuno, Nagoya University, Japan Manuel Mazzara, Innopolis University, Russia Per Håkon Meland, SINTEF ICT, Norway Carlos Julian Menezes Araujo, Federal University of Pernambuco, Brazil Hugo Miranda, University of Lisbon, Portugal Shivakant Mishra, University of Colorado at Boulder, USA Costas Mourlas, National and Kapodistrian University of Athens, Greece Francesc D. Muñoz-Escoí, Universitat Politècnica de València, Spain Jogesh K. Muppala, The Hong Kong University of Science and Technology, Hong Kong Jun Na, Northeastern University, China Syed Naqvi, Birmingham City University, United Kingdom Sarmistha Neogy, Jadavpur University, India Mats Neovius, Åbo Akademi University - Turku, Finland Dimitris Nikolos, University of Patras, Greece Satoru Ohta, Toyama Prefectural University, Japan Hong Ong, MIMOS Bhd, Malaysia Frank Ortmeier, Otto-von-Guericke-Universität Magdeburg, Germany Roberto Palmieri, Virginia Tech, USA

Andreas Pashalidis, Katholieke Universiteit Leuven - iMinds, Belgium Antonio Pecchia, Federico II University of Naples, Italy Giancarlo Pellegrino, Saarland University, Germany Ronald Petrlic, Saarland University, Germany Alfredo Pironti, INRIA Paris Rocquencourt, France Peter T. Popov, City University London, UK Wolfgang Pree, University of Salzburg, Austria Chi-Man Pun, University of Macau, Macau S.A.R., China Feng Qin, Ohio State University, USA Ruben Rios, University of Málaga, Spain Luigi Romano, University of Naples Parthenope, Italy Francesca Saglietti, University of Erlangen-Nuremberg, Germany Dimitri Scheftelowitsch, TU Dortmund University, Germany Hans-Peter Schwefel, FTW Forschungszentrum Telekommunikation Wien GmbH, Austria / Aalborg University, Denmark Sahra Sedighsarvestani, Missouri University of Science and Technology, U.S.A. Jean-Pierre Seifert, Technische Universität Berlin & Telekom Innovation Laboratories, Germany Bruno Sericola, INRIA, France Dimitrios Serpanos, University of Patras & ISI, Greece Muhammad Shafique, Karlsruhe Institute of Technology (KIT), Germany Kuei-Ping Shih, Tamkang University, Taiwan Francois Siewe, De Montfort University, UK Navjot Singh, Avaya Labs Research, USA Sean Smith, Dartmouth College, USA Arun Somani, Iowa State University, USA Alessandro Sorniotti, IBM research - Zurich, Switzerland George Spanoudakis, City University London, U.K. Avinash Srinivasan, George Mason University, USA Kuo-Feng Ssu, National Cheng Kung University, Taiwan Manolis Stamatogiannakis, VU University Amsterdam, Netherlands Vladimir Stantchev, Berlin Institute of Technology, Germany Dimitrios Stratogiannis, National Technical University of Athens, Greece Jingtao Sun, National Institute of Informatics, Japan Neeraj Suri, TU-Darmstadt, Germany Kenji Taguchi, National Institute of Advanced Industrial Science and Technology (AIST), Japan Oliver Theel, University Oldenburg, Germany Sergio Pozo Hidalgo, University of Seville, Spain Kishor Trivedi, Duke University - Durham, USA Elena Troubitsyna, Åbo Akademi University, Finland Timothy Tsai, Hitachi Global Storage Technologies, USA Sara Tucci-Piergiovanni, CEA List, France Marco Vallini, Politecnico di Torino, Italy Ángel Jesús Varela Vaca, University of Sevilla, Spain Bruno Vavala, Carnegie Mellon University, USA | University of Lisbon, Portugal Phan Cong Vinh, Nguyen Tat Thanh University, Vietnam Lucian Vintan, Lucian Blaga University of Sibiu, Romania Hironori Washizaki, Waseda University, Japan Eduard Weber, University of Duisburg-Essen, Germany

Charles B. Weinstock, Software Engineering Institute - Carnegie Mellon University, USA Byron J. Williams, Mississippi State University, USA Victor Winter, University of Nebraska at Omaha, USA Dong Xiang, Tsinghua University, China Chun Jason Xue, City University of Hong Kong, Hong Kong Hiroshi Yamada, Keio University, Japan Toshihiro Yamauchi, Okayama University, Japan Chao-Tung Yang, Tunghai University, Taiwan Liu Yang, Nanyang Technological University, Singapore Piyi Yang, University of Shanghai for Science and Technology, China II Yen, University of Texas at Dallas, U.S.A Hee Yong Youn, Sungkyunkwan University, Korea

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

## **Table of Contents**

| Integrating Security Consideration Into a Safety Case Construction<br>Elena Troubitsyna                                           | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Static Worst-Case Execution Time Analysis Tool Development for Embedded Systems Software <i>Thomas Jerabek and Martin Horauer</i> | 7  |

| Expurgated Codes for Detecting Jamming in Multi-level Memories<br>Yaara Neumeier and Osnat Keren                                  | 15 |

| Safe Transitions of Responsibility in Highly Automated Driving<br>Rolf Johansson, Jonas Nilsson, and Martin Kaalhus               | 21 |

## **Integrating Security Considerations Into a Safety Case Construction**

Elena Troubitsyna Åbo Akademi University Tuomionkirkontori 3, 20500 Turku, Finland e-mail: Elena.Troubitsyna@abo.fi

Abstract— Wide-spread reliance on networking in modern safety-critical control systems makes security increasingly interwoven with safety. Hence, we need novel methodologies integrating security consideration into the process of system development and safety case construction. Safety case is a structured argument justifying system safety. In this paper, we propose an approach that relies on the systems-theoretic analysis to construct security-aware safety cases. We define a number of generic patterns facilitating definition of securityaware safety cases. Our approach allows the developers to analyse the mutual interdependencies between safety and security in the design of networked control systems. It provides the engineers with a systematic top-down method for deriving constraints that should be imposed on the system and software behavior to guarantee safety in the presence of accidental and malicious faults.

Keywords-safety case; systems-theoretical approach; controlling software; security; integrated analysis

## I. INTRODUCTION

Traditionally safety-critical systems have been considered as closed systems that should ensure safety despite (accidental) components faults [1]. However, increasing openness and reliance on networking has introduced security attacks, i.e., malicious faults, as an important factor to be analyzed in the process of system development and verification [2].

Since safety and security are often considered as separate fields, there is a lack of integrated approaches that support the holistic analysis of software-intensive systems that can guarantee safety in presence of both malicious and accidental faults [1]. However, recent research experiments have demonstrated, e.g., that cars security vulnerabilities allow to remotely override safety functions and take control over break and steering [3]. Therefore, there is a clear need for the approaches that provide the developers with an integrated view on system safety and security.

In this paper, we propose an approach to integrating the security consideration into the process of safety case construction for networked safety-critical control systems.

Safety case is a structured argument about system safety [4]-[8]. Often, it is defined using Goal Structuring Notation [9]. While constructing a safety case, we explicitly define the links between top-level goal of achieving system safety

and the satisfaction of constraints that should be imposed on the system design to achieve it.

To derive safety and security constraints required for achieving safety, we propose to employ the systemstheoretic analysis [10]. Systems theory considers the problem of ensuring safety as a control problem and as such, provides us with a more inclusive model of accident causality. Therefore, the systems-theoretic perspective supports an integrated consideration of safety and security constraints that are essential in designing networked control systems.

In this paper, we demonstrate how an application of the systems-theoretic analysis allows us to define the main classes of causes that might lead to unsafe behavior and define the corresponding safety goals. By top-down decomposition of such goals, we define safety and security constraints that should be imposed on the system design to guarantee safety. We define the patterns of safety case fragments that allow us to justify safety in presence of both accidental and malicious faults.

We believe that an application of the proposed approach enables holistic analysis of safety and security interdependencies and facilitates construction of safe networked control systems.

The paper is structured as follows: in Section II, we introduce the notion of the safety case and the Goal Structuring Notation. In Section III, we describe the principles of systems-theoretical analysis. In Section IV, we present our approach to constructing security-aware safety cases using systems theory. In Section V, we overview the related work. Finally, in Section VI, we discuss the proposed approach.

### II. SAFETY CASES

A safety case is "a structured argument, supported by a body of evidence that provides a convincing and valid case that a system is safe for a given application in a given operating environment" [4] [5].

The construction, review and acceptance of safety cases are the important steps in safety assurance process of safetycritical systems. Several standards, e.g., ISO 26262 [6] for the automotive domain, EN 50128 [7] for the railway domain, and the UK Defense Standard 00-56 [8], prescribe production and evaluation of safety (or more generally assurance) cases for certification of such systems.

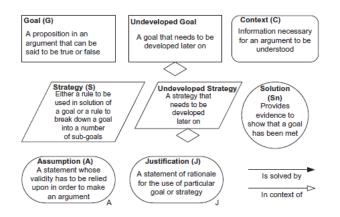

Figure 1. Basic elements of GSN.

A safety case can be defined textually or graphically. Currently, Goal Structuring Notation (GSN) – a graphical notation proposed by Kelly [9] – is getting increasingly popular for describing safety case. GSN aims at a graphical representation of safety case elements as well as the relationships that exist between these elements. The main building blocks of GSN are shown in Figure 1.

Essentially, a safety case constructed using GSN consists of goals, strategies and solutions. Here goals are propositions in an argument that can be said to be true or false (e.g., claims of requirements to be met by a system). Solutions contain the information extracted from analysis, testing or simulation of a system (i.e., evidence) to show that the goals have been met. Finally, strategies are reasoning steps describing how goals are decomposed and addressed by subgoals. Thus, a safety case constructed in GSN presents a decomposition of the given safety case goals into the subgoals until they can be supported by the direct evidence (a solution). It also explicitly defines the argument strategies, relied assumptions, the context in which goals are declared, as well as justification for the use of a particular goal or strategy.

The elements of a safety case can be in two types of relationships: "Is solved by" and "In context of". The former is used between goals, strategies and solutions, while the latter links a goal to a context, a goal to an assumption, a goal to a justification, a strategy to a context, a strategy to an assumption, a strategy to a justification.

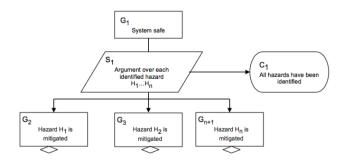

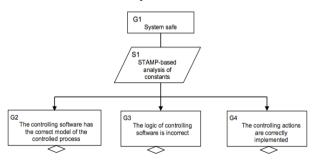

A typical high-level structure of the safety case is shown in Figure 2. The high-level goal **G1** contains the proposition that the system is safe. The strategy **S1** is to decompose toplevel goal into lower level subgoals **G2-G**<sub>N+1</sub> aiming at demonstrating that each individual hazard has been mitigated. The safety case is valid under the assumption **C1** that all hazards have been identified.

Usually, to achieve completeness of hazard identification the developers rely on safety analysis, e.g., fault trees, Failure Modes and Effect Analysis, etc. However, Leveson [10] points out that such techniques rely on linear causality models and lack the power to exhaustively analyse

Figure 2. High-level safety case.

hazardous behaviour in complex software-intensive systems. She argues that we need to rely on systems-theoretic approaches to guarantee safety of such complex systems.

In complex software-intensive systems, hazards might be caused not only by accidental (i.e., non-malicious) component failures but also security failures caused by attacks on system network infrastructure, design errors, unforeseen component interactions, etc. Therefore, we need the integrated systems-theoretic approaches that allow us to identify the strategy for protecting the services and functions that are essential for ensuring system safety in presence of disruptions of various natures.

Next, we present a systems-theoretic approach to integrated reasoning about safety of complex networked systems that are subjects of accidental and malicious faults.

## III. SYSTEMS-THEORETIC APPROACH

Systems theory establishes foundations for engineering complex systems [11]. It provides a more inclusive model of accident causality called STAMP – System-Theoretic Accident Model and Processes [10]. STAMP envisions losses as resulting from interactions among humans, physical system components and the environment that lead to the violation of safety constraints. The main difference between STAMP and the traditional approaches to safety is that it shifts the focus from preventing failures to enforcing safety constraints on system behavior.

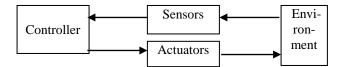

To illustrate the main principles of a systems-theoretic approach, let us consider let us consider a generic control system. A control system is a reactive system with two main entities: an environment and a controller. The environment behaviour evolves according to the involved physical processes and the control signals provided by the controller. The controller monitors the behaviour of the plant and adjusts it to provide intended functionality and maintain safety. The control systems are usually cyclic, i.e., at periodic intervals they get input from sensors, process it and output the new values to the actuators. The general structure of a control system is shown in Figure 3.

The controller is a hierarchical control structure that constraints the system behavior. Each layer of it enforces the required constraints on the behavior of the components at

Figure 3. A general structure of a control system.

Figure 4. Systems-theoretic view on control system.

the next lower level. The control loops operate between the layers. To achieve safety, we should guarantee that, under the hostile environmental conditions and in presence of accidental and malicious faults, the control actions prevent hazard occurrence.

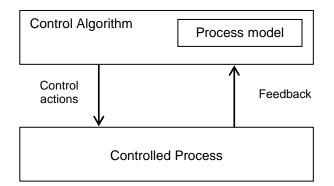

In systems and control theory, the controller contains a model of the process that it controls. Such a model serves as a basis for defining the necessary control actions, as shown in Figure 4. Hazards often occur as a result of inconsistencies between the controller's model of the controlled process and the actual process state.

By applying systems-theoretic analysis and analyzing the general structure of a control system, we can observe that safety can be violated due to three types of causes

- Controller cannot built a correct model of the process because the measurements provided by the sensors are invalid

- Controller has the correct model of the process but there is a logical error in implementing correct control actions

- The actuator fails to correctly implement the control actions.

This observation allows us to refactor our generic safety case pattern presented in Figure 1 as shown in Figure 5. It reflects the systems-theoretic approach to ensuring safety and establishes a systematic way for construct the safety case by further decomposition of subgoals G2-G4.

In the next section, we propose a systematic approach to analyzing how the accidental and malicious faults introduce inconsistencies into the controller's model of the process, distort the logic of the controller or prevent correct implementation of the controller actions.

## IV. SECURITY-INFORMED SAFETY CASES

Let us again consider the generic control cycle presented in Figure 3. For many control systems, safety can be formulated as the following proposition:

The value of critical parameter p always remains within safe boundaries.

To achieve this safety goal, we need to systematically analyse the causes that can introduce hazardous deviations in the controller's model of the process controlling p and the actual state of p.

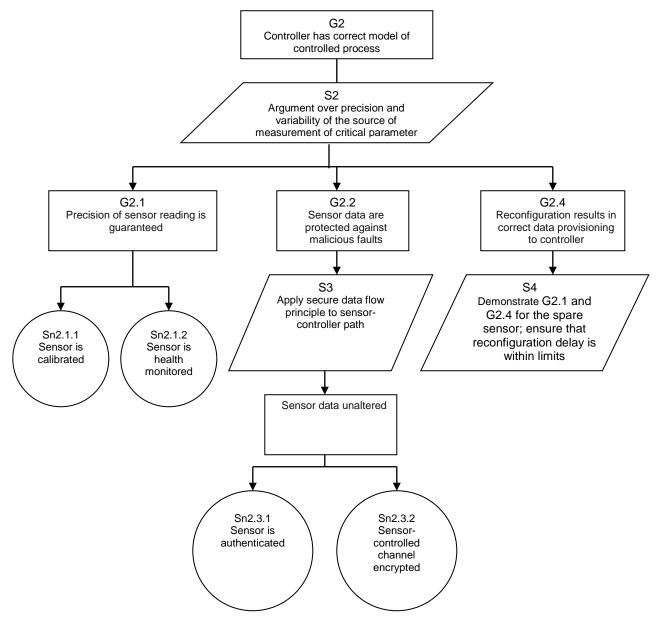

To build the corresponding model of the process, the controller relies on the measurement of p provided by the corresponding sensor. Therefore, the first condition for ensuring accuracy of the controller's model is validity of sensor's reading.

The sensor's readings can be distorted due to accidental faults of the sensor or security attacks. If the sensor fails and the controller does not detect it, then it starts to rely on wrong data. Hence, to guarantee safety, we should ensure that the sensor health is monitored and upon detection of failure the controller starts to rely on alternative reliable sources of measurement of p.

Figure 5. Systems-theoretic approach to safety case.

Typically, safety-critical control systems contain some form of redundancy. For instance, there might be hot or cold spare sensors. In the first case, the controller simply switches to obtaining readings from the spare sensor without any disruption in measurement provisioning. In the second case, a certain time interval is required to activate the cold spare. The system design should ensure that the time period required for the reconfiguration is sufficiently short, i.e., it would not introduce dangerous deviations in the controller's model of the process while the measurements are not available.

The controller might also obtain the invalid measurements of p due to security attacks. In the context of our control loop, it is relevant to consider the following security failures:

- spoofing the identity of sensor and

- tampering sensor data by attacking the communication channel between the sensor and the controller.

By spoofing the sensor identity the attacker can supply the controller with the deliberately wrong measurements of p. They can "trick" the controller into thinking that the value

Figure 6. Pattern for G2 decomposition.

of the controlled parameter is well within safety limits. This is a dangerous deviation of the controller's model of the process. Hence, it is very likely to result in hazard occurrence due to controller inability to issue the correct control commands required to maintain safe value of p. Tampering with sensor data has the same effect.

The analysis above demonstrates the direct impact of security on safety. The systems-theoretic approach allows us to identify the strategy for protecting the systems. Namely, we should guarantee that the source of measurement of p is authenticated and the communication link between the sensor and the controller is encrypted, i.e. does not allow for unauthorized data alternations. In the similar way, to ensure that the sensor failures are reliably detected, we need to guarantee that the health monitoring data is not tampered

with.

We can also demonstrate that safety-security interdependencies are sometimes conflicting and require trade-offs.

To ensure security, the design of software-intensive systems typically follows multi-level secure systems principle introduced by La Padula and Bell [12]. Often the designers consider two security levels: high, meaning highly sensitive or highly trusted, and low, meaning less sensitive or less trusted. When the trusted components of the system interact with the untrusted parts, one has to ensure that there is no indirect leakage of sensitive information from the trusted to untrusted part. Usually it is defined as no "downflow" policy. Such a security requirement is commonly

Figure 7. Pattern for G3 decomposition.

#### called secure information flow.

Let us consider how this principle is implemented in our case. As a result of the analysis above, we have derived the requirements that ensure no down flow policy for the sensor providing the measurements of p. Now, let us consider the case when the sensor providing the measurements of p has failed and the controller has to use the alternative sources of measuring p.

For the spare sensor, the system might not have the authentication and encryption procedure implemented and hence switching to the use of the alternative sensor would break the secure information flow policy. By preventing the use of measurements provided by the spare sensor, we leave the controller without the feedback required to build the adequate model of the controlled process. On the other hand, the use of unauthenticated sensor and unencrypted channel introduces security vulnerability. It is clear that we should resolve this conflict. For instance, we might run spare sensor authentication upon reconfiguration and require to use the encryption once the spare sensor becomes the primary source of measurements of p.

The system-theoretic analysis allows us to construct the corresponding part of the safety case, as shown in Figure 6.

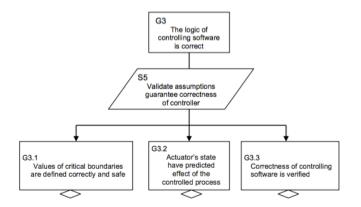

Now, let us discuss the constraints that should be imposed on the system to ensure that the goal **G3** is achieved. Essentially, we have to verify that the controller actions maintain the safety invariant "p is within safety boundaries". To verify this we have to introduce a number of assumptions.

The first class of assumptions explicitly states the impact of the actuator state on the value of the controlled parameter. Let us explain it by an example. Assume that the controlled parameter is a temperature *t*. The actual temperature should be kept within safety boundaries *t\_min\_crit* and *t\_max\_crit*.

The temperature is controlled by switching on and off the heater. The assumptions that we make is that when the heater is switched on the temperature is increasing. Correspondingly, when the heater is switched off the temperature is decreasing.

Another class of assumptions that we need to introduce deals with the inertia of the controlled physical process and relies on the cyclic behavior of the system. Since the controller receives the measurements of the controlled parameter once per control cycle, it needs to issue the control actions changing the state of the actuator before the critical boundaries are reached.

To demonstrate that the actual value of the parameter always remains within safety limits, we need to constrain  $\Delta$  - the maximum possible imprecision of the parameter in the process model as well as  $\Delta_{\max\_cycle}$  – the maximum possible change of the parameter per cycle.

The state of the actuator should be changed to the one that leads to the increase of the parameter at  $P_{min}$ , which is greater than  $p_{min}crit$  at least for the sum of  $\Delta$  and  $\Delta_{max_{cycle}}$ . The similar condition is imposed on  $P_{max}$ . Under these assumptions, we can verify that the controlling software maintains safety invariant, i.e., we can argue for achieving the goal **G3**. The corresponding fragment of the safety argument is shown in Figure 7.

Next, we investigate the constraints that should be imposed on the system to justify achieving goal G4. It is obvious that if the actuator fails and its failure remains undetected then it directly leads to failure to implement the commands of the controller in the correct way. Therefore, we should guarantee that the failures of the actuator are reliably detected and the system is put in a safe non-operational state upon it.

Now, let us consider the security-related constraints that should be satisfied to guarantee achieving goal **G4**. Even though the controller could have issued the correct control commands, due to spoofing controller identity or tampering commands the actuator might receive the incorrect settings that might breach safety. Therefore, we have to enforce secure data flow policy on the communication between the controller and the actuator as well. The corresponding fragment of the safety case is shown in Figure 8.

Figure 8. Pattern for G4 decomposition.

We can summarize the proposed methodology as follows:

- 1. Apply systems-theoretic approach to analyse how the controller builds the process model.

- 2. Define the top-level safety goal and identify critical parameters that should be monitored and controlled. Define safety conditions over these parameters.

- 3. Create an architectural model of the system and identify

- a. the components involved into providing input to the controller allowing it to build the process model (sensors)

- b. the components responsible for implementing controller actions (actuators)

- 4. For the identified components analyse the impact of failures and define the mitigation actions required to achieve safety goals. Construct the corresponding fragments of the safety case

- 5. Analyse data flow and define security constraints guaranteeing secure data flow policy for monitoring the critical parameters and implementing controller actions. Construct the corresponding fragments of the safety case

- 6. Derive the constraints required to verify correctness of the controller logic. Construct the corresponding fragment of the safety case.

#### V. RELATED WORK

Currently, the problem of integrated analysis of safety and security is receiving significant research attention. Schmittner at al. propose an approach that adapts Failure Mode and Effect and Criticality Analysis to address safety failures [13]. The work demonstrates how to take into account the motives of the intruder as well as costs and complexity of exploiting vulnerabilities. The approach proposed by Schmittner et al. can be used as an input for the safety case construction technique presented in this paper.

The approach relying of the integration of safety consideration into fault tree analysis has been proposed by Steiner and Liggesmeyer. The approach provides the engineering with a structured way to discover and analyse security vulnerabilities that have safety implications. This work complements the systems-theoretical approach to construction of the safety cases proposed in this paper.

Formal approaches proposed to study security and safety interactions typically focus on finding conflicts between safety and security requirements [15]. The majority of the approaches demonstrate how access control rules contradict safety requirements. In our approach, we do not contrapose safety and security but rather derive the security and safety constraints in top-down manner based on the safety cases. The advantage of our approach lies in its ability to capture the dynamic nature of safety and security, e.g., resulting from the reconfiguration required to achieve fault tolerance.

## VI. CONCLUSIONS

In this paper, we have proposed a systematic approach to construction of security-aware safety cases. In our approach, derivation of safety and security constraints proceed hand-inhand with safety case construction. The use of systemstheoretic reasoning allows us to derive the constraints required for providing arguments for safety case in a disciplined top-down way. Such an approach supports an integrated reasoning about safety and security that facilitates analysis of requirements interdependencies and explicit identification of trade-offs required to achieve safety in presence of both malicious and accidental failures.

In our future work, we are planning to validate the proposed approach in a number of industrial case studies as well as provide an automated tool support linking systemstheoretic analysis and safety case construction.

#### REFERENCES

- R. Bloomfield, K. Netkachova, and R. Stroud, "Security-Informed Safety: If It's Not Secure, It's Not Safe". Workshop on Software Engineering for Resilient Systems, LNCS 8166, Springer, Sept. 2013, pp. 17-32. DOI 10.1007/978-3-642-40894-6\_2.

- [2] W. Young and N.G. Leveson, "An integrated approach to safety and security based on systems theory". Communication of ACM 57(2), 31-35, 2014, DOI 10.1145/2556938.

- [3] Online http://www.bbc.com/news/technology-35841571. Accesed 02.04.2016.

- [4] T. Kelly and J. McDermid, "Safety case construction and reuse using patterns". 16th International Conference on Computer Safety, Reliability and Security (SAFECOMP'97), Springer-Verlag, Sept. 1997, pp. 55–96, doi: 10.1007/978-1-4471-0997-6\_5.

- [5] P. Bishop and R. Bloomfield, "A methodology for safety case development", in: Safety-Critical Systems Symposium, Springer-Verlag, Feb.1998, pp.10-16, , doi: 10.1008/243-1-3382-06577-5\_6.

- [6] International Organization for Standardization, ISO 26262 Road Vehicles Functional Safety, 2011.

- [7] European Committee for Electrotechnical Standardization (CENELEC), EN 50128 Railway Applications – Communication, Signalling and Processing Systems – Software for Railway Control and Protection Systems, 2011.

- [8] Defence Standard 00-56, UK Ministry of Defence. 00-56 Safety Management Requirements for Defence Systems, 2007.

- [9] T.P. Kelly, "Arguing safety -- a systematic approach to managing safety cases", PhD Thesis York University, UK, 1998.

- [10] N. Leveson, "Engineering a safer world: Systems thinking applied to safety". In MIT Press. 2011.

- [11] P.Checkland, Systems Thinking, Systems Practice. Wiley, 1981.

- [12] D.E.Bell and L.J LaPadula.. "Secure Computer Systems: Mathematical Foundations", Journal of computer Security, 1996, 4:239-263.

- [13] C. Schmittner, T. Gruber, P.P. Puschner, and E. Schoitsch, "Security application of failure mode and effect analysis (FMEA)". In: SAFECOMP 2014. LNCS 8666, Springer, Sept. 2014, pp. 310-325.

- [14] M. Steiner and P. Liggesmeyer, "Combination of Safety and Security Analysis - Finding Security Problems That Threaten The Safety of a System". Workshop on Dependable, Embedded and Cyber-physical Systems, Toulouse, France, 2013, pp.7-14.

- [15] P. Bieber and J. Brunel, "From Safety Models to Security Models: Preliminary Lessons Learnt", Workshops at SAFECOMP 2014, pp.269—281, DOI 10.1007/978-3-319-10557-4\_

## Static Worst-Case Execution Time Analysis Tool Development

## for Embedded Systems Software

Thomas Jerabek, Martin Horauer

University of Applied Sciences Technikum Wien Höchstädtplatz 6, A-1200 Vienna, Austria Email: {thomas.jerabek, martin.horauer}@technikum-wien.at

Abstract—Analyzing the worst-case execution time of embedded systems software is useful for assessing parameters like schedulability, performance (especially with regard to deadlines), etc. A commonly accepted approach to obtain these values is by way of static analysis that uses the software along with a model of the target processors architecture. This paper describes the required steps to construct a tool to assess the worst-case execution time of a given application with the help of an opensource framework. The ensuing evaluation provides a comparison of the results with other approaches. In addition, this paper can be used as guide to implement an instruction set architecture of a target processor in order to enable various static analyses with the aim to estimate the worst-case execution time.

Keywords—architecture description language; instruction set simulator; worst-case execution time analysis.

#### I. INTRODUCTION

Embedded systems nowadays are ubiquitous in our daily life. One kind of embedded systems are real-time systems where the correct operation of the system depends on the logical correctness of the computations and upon the time at which the result is produced. Hence, knowledge about execution times – and here in particular the worst-case execution time (WCET) – is of relevance, e.g., to assess whether deadlines imposed by application requirements will be met, or to assess the schedulability of an implementation.

The WCET defines the longest time it takes to execute a program on a specific target processor. There are different ways to determine this value.

(1) One method uses static code analysis [1], [2] by way of a model of the processor's architecture. In fact, various analyses are in use therefore, e.g.:

- Control-flow analysis

- Value analysis

- Cache analysis

- Pipeline analysis

- Path analysis

- WCET estimation

Each of these analyses must be implemented and adapted for every new target architecture.

(2) Another WCET analysis method is measurement-based where the execution time of an application, function or task is recorded during runtime. To that end, the source code must be instrumented to provide suitable triggers for the measurement and appropriate stimuli are required to stress worst-case behavior. In practice, the latter requires elaborated test-setups [3], [4].

(3) The third approach combines both the static analysis method to evaluate input data and the measurement-based method to estimate the WCET [3].

Independent of the chosen approach, it is essential that the real WCET is never longer than the evaluated value and the result is as close as possible to the reality. These two aspects describe a safe and tight WCET evaluation.

Dependable systems have the ability to avoid service failures, which are unacceptable in terms of frequency and severity. Many aspects need to be considered in order to ensure such a behavior; however, this paper focuses on a specific detail: predictable execution times of dependable software (e.g., a hard real-time system) via WCET analysis. Such an analysis is an inherent part of the safety process during the design and development of automotive and avionics systems to avoid timing issues [5], [6]. For example, unmanned aerial vehicle (UAV) software contains various tasks (e.g., engine control or position sensing) where the knowledge about their WCET is mandatory for safe operation.

The contribution of this paper presents a generic approach of how to enable WCET analysis for a modern processor architecture following approach (1) using static analysis of executable binaries. Besides the architecture module, two analysis tools were implemented using the OTAWA framework's API. The result is a useful guide to implement WCET analysis for a certain processor architecture. It can be utilized for WCETaware development to prevent systematic failures in order to increase the reliability of a dependable system.

The structure of the paper is as follows. First, we detail typical design patterns and their effect on WCET using some examples. Next, we present related work in Section III, followed by a description of the implementation in Section IV. Section V provides some benchmarks, and finally, a use case is presented in Section VI before we conclude the paper in Section VII.

## II. WCET ESTIMATION OF EMBEDDED SYSTEMS SOFTWARE

Software for embedded systems typically follow either a bare-bone approach or employ some kind of (real-time) operating system. Bare-bone applications in turn either follow a super-loop architecture or a fore-/background approach [7]. When using a preemptive operating system task and/or thread models are in place. Below, we will use these patterns and show how WCET can be estimated by way of examples. This not only gives an insight on the analysis itself, but also encourages the technical background for the further chapters.

In general, static WCET evaluation is based on one of the three present calculation techniques: (1) path-based [8], (2) tree-based [9], and (3) implicit path enumeration technique (IPET) [10]. Since these approaches are usually applied on instructions or basic blocks, they need to be abstracted in order to use them for a higher program representation. The aim of this chapter is to describe the WCET of a program with a formalism using its most basic elements. This highlevel formalism is inspired by the path-based approach where the WCET will be determined by first calculating times for different paths within a program and then looking for the path with the longest execution time. It consists of a header  $T_H$ and a content/path  $T_P$  that is multiplied with its loop-bound LB, as shown in (1). Depending on the programs structure, this basic equation needs to be adapted. All subsequent Tvariables are already defining the maximum execution time of the corresponding program part as processor clock cycles. This means, that the result is independent of the processors frequency; however, one can convert it into a time via dividing it by the processors clock rate.

$$WCET = T_H + T_P * LB \tag{1}$$

**Bare-bone** program structures consist of an initialization part  $T_{IN}$  and an endless loop  $T_L$ . The execution time of the latter equals a cycle time, which is especially relevant for super-loop architectures because they are not using interrupts at all and only detect events via requests (polling). It can be used as maximum response time for a certain event and can be evaluated as shown in (2).

$$WCET_P = T_P = T_L \tag{2}$$

The other kind of bare-bone applications is using an interrupt driven fore-/background architecture. Here, interrupts and the execution of their associated service routines (ISR) need to be considered for WCET evaluation. With its WCET and the execution rate, one can calculate an expected rate (periodicity) relative to the program under analysis. Depending on the referenced program section  $T_{PS}$ , the interrupt rate, as estimated by (4), contains only the loop section or the entire application (see (3)). For the latter, interrupts need to be enabled before the program part under analysis. The sum of all interrupt service routines  $T_{SI}$  is estimated by adding up the expected timing of every interrupt as shown in (5). The equation assumes that all involved interrupts are activated permanently.

$$T_{PS} = T_L \lor (T_{IN} + T_L) \tag{3}$$

$$R_I = \frac{I_{PS}}{expected \, ISR \, Rate} \tag{4}$$

$$T_{SI} = \sum_{i \in SI} [T_{Ii} * R_{Ii}] \tag{5}$$

The WCET of one loop cycle of interrupt driven applications takes the interrupts into account and can be estimated by (6). The overall WCET is the result for termination after a certain number of cycles specified by the loop-bound (see (7)).

$$WCET_P = T_P = T_L + T_{SI} \tag{6}$$

$$WCET = T_{IN} + T_P * LB \tag{7}$$

An example is given for a fore-/background structure with 3 interrupt service routines. The WCET of one loop cycle should be estimated. Worst-case time behaviors of each individual part were already evaluated as listed below.

$$T_{IN} = 600 \ clock \ cycles$$

$$T_P = 9000 \ clock \ cycles$$

$$T_{I1} = 250 \ clock \ cycles$$

$$T_{I2} = 890 \ clock \ cycles$$

$$T_{I3} = 60 \ clock \ cycles$$

We assume three ISRs with the following shortest possible periodicity:

- ISR1: executed every 5000 clock cycles

- ISR2: executed every 20000 clock cycles

- ISR3: executed every 1400 clock cycles

Thus we get:

$$R_{I1} = \frac{9000}{5000} = 1.8 \approx 2$$

$$R_{I2} = \frac{9000}{20000} = 0.45 \approx 1$$

$$R_{I3} = \frac{9000}{1400} = 6.43 \approx 7$$

$$T_{SI} = 250 * 2 + 890 * 1 + 60 * 7 = 1810 \ clock \ cycles$$

$$WCET_P = 9000 + 1810 = 10810 \ clock \ cycles$$

The result shows that an increasing number of interrupts significantly affects the WCET.

**RTOS:** There are major differences between bare-bone and real-time operating system (RTOS) structures, such as the administrative overhead and the interruption of execution by a higher priority task in real-time operating systems.

When assuming a priority based scheduler, it is a challenge to evaluate a task's WCET because each task, except the highest priority one, can be interrupted by a higher priority task. As a result, evaluation needs to be done by a top-down approach starting with the highest priority one. Equation (8) describes the maximum interruption time of a task by summing up both, all Tasks with a higher priority  $T_{HPT}$  and their administrative overhead  $T_{AO}$  (e.g., context switch, scheduling). The subsequent calculation is identical to bare-bone programs, as shown in (9) and (10).

$$T_{INT} = \sum_{i=1}^{n} T_{AOi} + \sum_{i=1}^{n} T_{HPTi}$$

(8)

$$WCET_P = T_P = T_L + T_{INT} \tag{9}$$

$$WCET = T_{IN} + T_P * LB \tag{10}$$

For tasks using an endless-loop pattern, the worst-case cycle time  $WCET_P$  is typically the most relevant. The overall WCET is the result for termination after a specified number of cycles (loop-bound). For tasks using a run-to-completion

pattern there are typically no cycles and, therefore, the loopbound equals 1 for the overall WCET.

An example calculation follows for a run-to-completion task, which is implemented into a real-time operating system where 2 tasks with a higher priority are existing. The task's entire WCET should be determined with the assumption that the administrative overhead is task independent. Worst-case time behaviors of each individual part were already evaluated as listed below.

$$\begin{split} T_{IN} &= 200 \ clock \ cycles \\ T_L &= 3900 \ clock \ cycles \\ T_{HPT1} &= 2320 \ clock \ cycles \\ T_{HPT2} &= 1100 \ clock \ cycles \\ T_{AO} &= 590 \ clock \ cycles \end{split}$$

This results in:

$$\begin{split} T_{INT} &= 590 + 590 + 2320 + 1100 = 4600 \ clock \ cycles \\ T_P &= 3900 + 4600 = 8500 \ clock \ cycles \\ WCET &= 200 + 8500 = 8700 \ clock \ cycles \end{split}$$

The outcome of 8700 cycles shows that the RTOS as well as tasks with a higher priority have a major impact on the tasks WCET.

## III. RELATED WORK

In the following, we provide a short comparison of (1) existing WCET analysis tools (cf. Table I) and further on (2) describe related architecture description languages (ADLs).

|              | nd.1                  | in the second second                                                                                                                                                                                                                                                                                                                                 | E                                                     | AL AL                                                 |

|--------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| aij          | 2000                  | 2:00                                                                                                                                                                                                                                                                                                                                                 | AS.                                                   | 5                                                     |

| Х            | $\checkmark$          | Х                                                                                                                                                                                                                                                                                                                                                    | $\checkmark$                                          | $\checkmark$                                          |

| $\checkmark$ | $\checkmark$          | Х                                                                                                                                                                                                                                                                                                                                                    | $\checkmark$                                          | $\checkmark$                                          |

| Х            | Х                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | Х                                                     | Х                                                     |

| $\checkmark$ | $\checkmark$          | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | $\checkmark$                                          | $\checkmark$                                          |

| $\checkmark$ | Х                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | Х                                                     | √*                                                    |

| Х            | Х                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | Х                                                     | $\checkmark$                                          |

| √**          | √**                   | X***                                                                                                                                                                                                                                                                                                                                                 | Х                                                     | $\checkmark$                                          |

| $\checkmark$ | $\checkmark$          | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | $\checkmark$                                          | $\checkmark$                                          |

| $\checkmark$ | Х                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | Х                                                     | Х                                                     |

| $\checkmark$ | Х                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                         | Х                                                     | Х                                                     |

|              | ✓<br>X<br>✓<br>✓<br>X | $\begin{array}{c c} \checkmark & \checkmark \\ X & X \\ \hline & \checkmark & \checkmark \\ \hline \checkmark & X \\ \hline & \chi & X \\ \hline & \checkmark & \chi \\ \hline & \checkmark & \chi \\ \hline & \checkmark & \checkmark \\ \hline & \checkmark & \chi \\ \hline & \checkmark & X \\ \hline \\ \hline & \checkmark & X \\ \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

TABLE I. WCET ANALYSIS TOOL COMPARISON.

(\*Eclipse plugin, \*\*partly, \*\*\*not required)

The aiT WCET Analyzer [1] from AbsInt features an easy to use GUI with a straightforward configuration. It is able to compute tight bounds of a programs WCET using static analysis. One can choose between different integer linear programming (ILP) solvers (e.g., CPLEX), analysis options and output reports (e.g., HTML and XML). User defined annotations can be provided using the AIS/AIS2 language in order to define loop bounds and other program information. It fulfills the ISO 26262 as well as the DO-178B level A qualifications.

Bound-T [11] (originally developed by Tidorum Ltd. and now released as open-source) is a command-line tool that uses static analysis for the WCET estimation. Annotations can be provided by the user, although, loop bounds can be derived automatically. Unfortunately, cached memory or the parallelism of functional units cannot be specified making it hardly unsuitable for many modern processors.

RapiTime [12] uses a measurement-based approach for the WCET evaluation. It derives a structural model of the program and instruments the source code during the build process of a program. Afterwards, it performs all given tests and extracts the timing data via execution traces. To finish up, a prediction of the worst-case path and WCET is carried out by combining the obtained timing information and the structural model of the code. It fulfills both the DO-178B/C and ISO 26262 qualification. Since RapiTime does not rely on a processor model, it is usable for a lot of targets as long as they support a mechanism to extract execution traces.

The SWEdish Execution Time analysis tool (SWEET) [13] is a research prototype that offers best-case execution time (BCET), WCET and flow analysis. It uses a program representation called ALF (Artist Flow Analysis Language) in which either a binary or source code has to be converted for further processing. It implements a flow analysis of a given program to detect infeasible paths and loop bounds. The latter can be exported to aiT or RapiTime flow facts format enabling further analyses. A low-level analysis tool called low-sweet allows evaluating the WCET by its own.

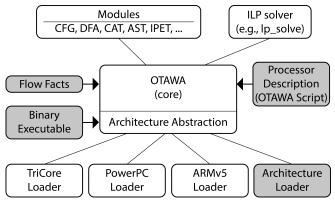

The Open Tool for Adaptive WCET Analysis (OTAWA) [14] is a static analysis framework that allows modifying, extending, or implementing analysis tools by using the OTAWA API. One of the existing tools, called OWCET, evaluates the WCET of a given program by providing the executable binary file, program flow information (flow facts) as well as a processor description (OTAWA script). With this information, it automatically links the corresponding architecture loader module and performs the analyses.

Besides RapiTime with its measurement-based approach, all of the mentioned tools use binary based static program analysis, which requires knowledge of the processor architecture in order to perform a timing analysis for WCET estimation. In fact, implementing support for a new target system requires the implementation/adaption of elaborate analyses to this new architecture.

At the core therefore, are usually architecture description languages (ADLs) that describe the processor model. They have a wide range of application; a majority is the generation of target specific tools (e.g., compiler or simulator). They are also used for the development and rapid prototyping of application-specific instruction-set processors (ASIPs).

There are different ADLs available to create an instruction set simulator (e.g., EXPRESSION [18], LISA [19] and nML [20]), however each of them describe the instruction set architecture of a specific processor family without detailed information of the microcontroller. This makes it possible to use the simulator for every microcontroller with the chosen processor architecture. For timing analyses, there are some details like cache or pipeline behavior missing at this point; therefore, this information is provided via additional description by the developer or end user. Hardware ADLs are likewise known as processor or machine description language and are not only used for simulators but also for processor development [21, p. 2].

These architecture description languages are classified in

three content-based (structural, behavioral and mixed) as well as four objective-based categories (compilation, simulation, synthesis and validation). This classification allows developers to choose an ADL by either content (e.g., instruction-set description) or purpose (e.g., generation of an instruction-set simulator). Due to the fact that not all ADLs can describe the instruction-set behavior with a detailed timing model, only a few are usable for WCET analysis.

Modeling a processor based on the ARMv5 architecture using the ArchC ADL is described in [15]. They divided the implementation into three phases, starting with the choice of a suitable ADL, followed by constructing of a toolchain (e.g., compiler and simulator) for the architecture; and phase three, analyzing the executed instructions by the simulator using program patterns. Their aim was to evaluate often used instruction patterns that can be merged to a new complex instruction in order to increase the performance.

A retargetable software timing analyzer for WCET estimation using the EXPRESSION ADL for processor models is described in the work of [16]. For their case study, a MIPS processor including its instruction set architecture was modeled and evaluated.

An approach for generating instruction set simulators from an enhanced nML architecture description is presented in [17]. The tool generates a simulator usable for static analysis. For demonstration purposes, their tool was applied to an ARMv5 architecture implementation.

For the approach described here, we choose the SimnML/nMP formalism in order to create an ARMv7E-M instruction set simulator. Sim-nML is an extension of the nML formalism with the purpose to perform efficient simulations; and the Macro Preprocessor (nMP) extends the Sim-nML syntax (e.g., recursive macros or macro calls within macros) in order to simplify the implementation. OTAWA is the chosen platform for the WCET evaluation because it is expendable, allowing to integrate new architectures and analysis tools. The decision to use a static code analysis approach was based on the requirements of the R&D project, which is intended to extend the analysis environment with other static analyses (e.g., stack usage, control-flow graph) at a later stage. A more detailed description of this choice is given in Section IV.

#### IV. IMPLEMENTATION

The OTAWA framework features an architecture abstraction layer, enabling to use the analysis framework independently of the actual target platform. This layer applies an architecture plug-in as an interface to the corresponding architecture loader, which contains all relevant details for the instruction set simulation.

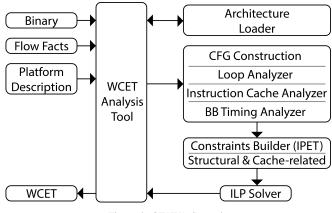

Figure 1 shows the structure of the OTAWA framework and highlights the mentioned concept of hardware abstraction by binding modules for the TriCore, PowerPC or ARMv5 architecture towards this layer. The OTAWA core links all modules including a set of analyses (e.g., data flow analysis), graph generation (e.g., control-flow graph), providing an abstract representation of the program as well as accessing an external ILP solver (e.g., lp\_solve). From a programmer's perspective, the architecture loader together with a processor description in the form of an OTAWA script are necessary to support WCET analyses for a certain processor. These two

Figure 1. OTAWA Structure

components are highlighted on the right side in Figure 1. One can use the OTAWA framework to perform WCET analyses by providing the binary executable and the flow facts of a program, as shown on the figure's left side. An overview of the necessary implementation steps is given below:

- 1) Description of the instruction set architecture as loader module.

- 2) Implementation of an interface for the architecture abstraction layer in order to link the loader module to the OTAWA framework.

- 3) Creation of a script for the target processor.

- 4) Adaption and extension of the analysis tool if additional features are desired.

- 5) Verification of the implementation.

The next sub-sections describe our implementation of the mentioned steps in a generic manner. Starting with step one and two in Section IV-A, followed by the processor script in Section IV-B as well as two tools (MKFFX and OSWA) in Section IV-C and Section IV-D that are using the OTAWA framework for evaluating a programs WCET, flow facts and basic block statistics. Details of our concrete implementation are given in Section IV-E, and finally, the verification is explained in Section IV-F.

## A. Architecture Loader

This module is the core part of the work presented in this paper and includes a description of the processor architecture in form of the instruction set. Most of the code was written in the Sim-nML/nMP language including information of the syntax, the binary representation and the semantics of each instruction from the architecture. The syntax is important for the disassembler output and control-flow graph because it is the representation of the assembler syntax. The image is used for linking the bits of a decoded instruction to the corresponding parameter (e.g., register or immediate value). Within the action part, the parameters from the image are used for describing the instruction's function. This means that calculations (e.g., shift or add), writing and reading registers, as well as updating flags is part of the action.

Beside the instructions themselves, there are registers, conditions, modes and exceptions within the Sim-nML/nMP part. Additionally, macros were defined to decrease the implementation effort and at the same time increase the readability. The rest of the implementation, containing auxiliary functions and algorithms, was written in the C-language. Afterwards, the

Generator of Libraries for Instruction Set Simulators (GLISS) was used to generate a C-library out of both implementation parts. This library along with the ARM module from OTAWA serve as input for the generation of the instruction set simulator, a so-called "architecture loader". In a final step, it was necessary to define the instructions kind (e.g., ALU or branch), target, semantic and used registers within the OTAWA ARM module in order to interpret each instruction correctly. All relevant architecture information for the work can be found in the corresponding architecture reference manual.

## B. Processor Script

This section describes the implementation of processor characteristics as OTAWA script, so that applications targeting a specific microcontroller can be analyzed with the OTAWA framework. The script is written in XML format and consists of several files, each for one component of the processor. The separation is described by the following listing:

- Main: This file is usually named after the microcontroller and includes information about the used architecture. It links all parts of the platform description (e.g., memory) and allows to configure items to finetune the analysis. In addition, necessary analysis steps can be included, which are accessible through the OTAWA API (e.g., BB\_TIME\_FEATURE ensures that the execution time computation of each basic block has been performed).

- Memory: The processor's different memory banks with their properties are described in this file. A typical description of a memory bank includes a name, the start address and its size, followed by the type (e.g., FLASH or SRAM). Read/write latencies can be defined in order to set a number of cycles for accessing or writing the memory. This is especially relevant for external memories with high access times. Finally, one can specify if a memory is writable or cachable.

- Pipeline: This file describes the processor's pipeline as big picture because its complexity is in many cases not describable. Each stage is described by an ID, a name, a width defining the number of parallel processed instructions, a latency for multi-cycle operations and a type. The type is typical *fetch* for the very first stage (e.g., instruction fetch from memory) and *commit* for the very last stage to declare the exit. In between, there are either lazy stages (e.g., decode) waiting for a defined time as well as execution stages. It is possible to define functional units for the execution stages (e.g., arithmetic logic or floating-point unit), allowing to link certain types of instructions to them.

- Cache: The processor's caches are described in this part. It is possible to state data, instruction or unified caches, whereby the elements are all the same. Each configuration consists of a replacement policy (e.g., LRU or FIFO), the size of a cache block, the number of blocks in each set and the number of sets in the cache. Additionally, different levels of cache can be defined.

It is essential to create a script for any used microcontroller as already small differences can result in a WCET deviation.

## C. Flow Facts Evaluation Tool

Since the exact control flow of a program depends on input data, it is impossible to make an estimation without program execution. So-called flow facts, include program flow information like maximum loop iteration counts (loop bounds) or recursion depths and are provided by the user. These details improve the precision of the analysis result; often they are necessary to evaluate a program's WCET at all. In cases where no explicit limitations (e.g., loop bound depends on input parameter) are given, either the user defines high but safe bounds (e.g., maximum value of the parameter's data type), which makes the WCET result inaccurate, or the estimation is infeasible. Defining the flow facts by hand is exhausting and imply a risk of incompleteness. Therefore, some analysis tools can automatically detect flow facts and save them into a respective file. The task of filling in missing information (e.g., boundary for a found loop) remains to be done prior to the evaluation of the WCET.

The introduced tool, called mkffx, generates flow facts in XML format by combining various input methods. First, it reads possibly existing flow facts from a given file and saves them in an internal representation, followed by analyzing the binary file to detect and record loops and other control information. Next, it will invoke the oRange tool [22], which analyzes loop bounds and extracts flow facts from the source code. This is an optional feature, since the source code is not available in every use case. Afterwards, the mkffx tool merges all results and outputs the flow facts. In this way, it reduces the necessary effort of describing them by hand because the combination of several inputs increases the rate of automatically detected loop bounds. Our mkffx tool extends the features of the mkff tool, which already comes with the OTAWA framework.

## D. WCET Analysis Tool

Evaluating a programs WCET takes several analysis steps which can vary depending on the processors architecture. Figure 2 shows a typical scenario of a WCET estimation using OTAWA.

Figure 2. OTAWA Scenario

The very first step is to load the program under analysis in the form of the binary executable as well as its flow facts information and the corresponding processor script (platform description). Next, the program from the binary file is transformed into an internal representation using the architecture loader and the CFG builder constructs its control-flow graph. Afterwards, analyses are applied starting with the loop analyzer which uses the loop boundaries from the provided flow facts. The platform description is taken into account to analyze the instruction caches behavior. With this information, the execution time of each basic block can be calculated. Sets of graph flow constraints (e.g., program flow and basic-block execution time bounds) are built for the implicit path enumeration technique (IPET) based calculation approach. These constraints are transformed into an integer linear programming problem with a goal function (WCET) and then solved using an external solver (e.g., lp\_solve). In the end, the analysis tool can output the resulting WCET. The OTAWA framework includes all of the mentioned modules as shown in Figure 1.

The OTAWA Stack and Worst-case execution time Analysis (OSWA) tool combines several features into one application. Beside the two main functions derived from its name: stack usage evaluation and WCET analysis, it can generate a controlflow graph with various output kinds and creates a basic block timing statistic. The latter allows identifying the most time consuming basic blocks within a given function or code snippet. An additional feature is the calculation of a ratio between the time spent inside and outside the function, which can be used to find out how much time is spent in sub-functions. For this paper, the WCET analysis feature is the most important one. OSWA performs the analysis of a specified function from a given binary file by involving flow facts and a processor description (OTAWA script). Our OSWA tool extends the features of the owcet tool, which already comes with the OTAWA framework.

#### E. Specific Implementation for the Use Case

The goal of our work is to enable WCET analysis for software targeting ARM Cortex-M4 processors. For this reason, the implementation in Section IV-A was accomplished for the ARMv7E-M architecture. It features the Thumb-2 technology with both, 16 and 32 bit operations. This architecture loader is based on an existing ARMv5 loader because its 16 bit Thumb instructions are mostly equivalent with the ARMv7 technology.

The Infineon XMC4500-F100K1024 microcontroller features an ARM Cortex-M4 processor core and was chosen for further evaluation (see Section VI). Its characteristics were described in the form of an OTAWA script as presented in Section IV-B.

#### F. Verification

As described in Section IV-A, the architecture implementation is split in a Sim-nML/nMP description and code written in the C language. As a result of the build process, a C-library that contains both parts is generated. This entire implementation as well as Sim-nML/nMP parts were verified using simulation, code reviews, and disassembler output comparison. The verification of the C parts is completed with the following methods: model checking, static code analysis, and test drivers based on boundary value analysis and equivalence class partitioning. In addition, a plausibility check of the implementation was performed by comparing WCET results of selected test cases with measurements and results from another tool, as shown in the subsequent section.

## V. BENCHMARKS