# VALID 2011

## The Third International Conference on Advances in System Testing and Validation Lifecycle

ISBN: 978-1-61208-168-7

October 23-29, 2011

Barcelona, Spain

## VALID 2011 Editors

Teemu Kanstrén, VTT Technical Research Centre of Finland - Oulu, Finland

## VALID 2011

## Forward

The Third International Conference on Advances in System Testing and Validation Lifecycle (VALID 2011), held on October 23-29, 2011 in Barcelona, Spain, continued a series of events focusing on designing robust components and systems with testability for various features of behavior and interconnection.

Complex distributed systems with heterogeneous interconnections operating at different speeds and based on various nano- and micro-technologies raise serious problems of testing, diagnosing, and debugging. Despite current solutions, virtualization and abstraction for large scale systems provide less visibility for vulnerability discovery and resolution, and make testing tedious, sometimes unsuccessful, if not properly thought from the design phase.

The conference on advances in system testing and validation considered the concepts, methodologies, and solutions dealing with designing robust and available systems. Its target covered aspects related to debugging and defects, vulnerability discovery, diagnosis, and testing.

The conference provided a forum where researchers were able to present recent research results and new research problems and directions related to them. The conference sought contributions presenting novel result and future research in all aspects of robust design methodologies, vulnerability discovery and resolution, diagnosis, debugging, and testing.

We welcomed technical papers presenting research and practical results, position papers addressing the pros and cons of specific proposals, such as those being discussed in the standard forums or in industry consortiums, survey papers addressing the key problems and solutions on any of the above topics, short papers on work in progress, and panel proposals.

We take here the opportunity to warmly thank all the members of the VALID 2011 technical program committee as well as the numerous reviewers. The creation of such a broad and high quality conference program would not have been possible without their involvement. We also kindly thank all the authors that dedicated much of their time and efforts to contribute to the VALID 2011. We truly believe that thanks to all these efforts, the final conference program consists of top quality contributions.

This event could also not have been a reality without the support of many individuals, organizations and sponsors. We also gratefully thank the members of the VALID 2011 organizing committee for their help in handling the logistics and for their work that is making this professional meeting a success. We gratefully appreciate to the technical program committee co-chairs that contributed to identify the appropriate groups to submit contributions.

We hope the VALID 2011 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in system testing and validation.

We hope Barcelona provided a pleasant environment during the conference and everyone saved some time for exploring this beautiful city.

### VALID 2011 Chairs

#### **Advisory Chairs**

Andrea Baruzzo, Università degli Studi di Udine, Italy Cristina Seceleanu, Mälardalen University, Sweden Mehdi Tahoori, Karlsruhe Institute of Technology (KIT), Germany Mehmet Aksit, University of Twente - Enschede, The Netherlands Amirhossein Alimohammad, Ukalta Engineering - Edmonton, Canada

#### **Research Institute Liaison Chairs**

Juho Perälä, VTT Technical Research Centre of Finland, Finland Alexander Klaus, Fraunhofer Institute for Experimental Software Engineering (IESE), Germany Kazumi Hatayama, Nara Institute of Science and Technology, Japan Alin Stefanescu, University of Pitesti, Romania Vladimir Rubanov, Institute for System Programming / Russian Academy of Sciences (ISPRAS), Russia Tanja Vos, Universidad Politécnica de Valencia, Spain

### **Industry Chairs**

Abel Marrero, Daimler Center for Automotive IT Innovations - Berlin, Germany Sebastian Wieczorek, SAP AG - Darmstadt, Germany Eric Verhulst, Altreonic, Belgium

## VALID 2011

## Committee

#### **VALID Advisory Chairs**

Andrea Baruzzo, Università degli Studi di Udine, Italy Cristina Seceleanu, Mälardalen University, Sweden Mehdi Tahoori, Karlsruhe Institute of Technology (KIT), Germany Mehmet Aksit, University of Twente - Enschede, The Netherlands Amirhossein Alimohammad, Ukalta Engineering - Edmonton, Canada

#### VALID 2011 Research Institute Liaison Chairs

Juho Perälä, VTT Technical Research Centre of Finland, Finland Alexander Klaus, Fraunhofer Institute for Experimental Software Engineering (IESE), Germany Kazumi Hatayama, Nara Institute of Science and Technology, Japan Alin Stefanescu, University of Pitesti, Romania Vladimir Rubanov, Institute for System Programming / Russian Academy of Sciences (ISPRAS), Russia Tanja Vos, Universidad Politécnica de Valencia, Spain

#### VALID 2011 Industry Chairs

Abel Marrero, Daimler Center for Automotive IT Innovations - Berlin, Germany Sebastian Wieczorek, SAP AG - Darmstadt, Germany Eric Verhulst, Altreonic, Belgium

#### VALID 2011 Technical Progam Committee

Fredrik Abbors, Åbo Akademi University - Turku, Finland Jaume Abella, Barcelona Supercomputing Center (BSC-CNS), Spain Mehmet Aksit, University of Twente - Enschede, The Netherlands Amirhossein Alimohammad, Ukalta Engineering - Edmonton, Canada Giner Alor Hernandez, Instituto Tecnologico de Orizaba - Veracruz, México César Andrés Sánchez, Universidad Complutense de Madrid, España Cesare Bartolini, ISTI - CNR, Pisa, Italy Andrea Baruzzo, Università degli Studi di Udine, Italy Paolo Bernard, Politecnico di Torino, Italy Serge Bernard, UniversitÈ Montpellier 2, France Domenico Bianculli, University of Lugano, Switzerland Bruce Cockburn, University of Alberta -Edmonton, Canada Maurizio D'Arienzo, Seconda Università degli studi di Napoli, Italy Florian Deissenboeck, Technische Universität München - Garching, Germany Stefano Di Carlo, Politecnico di Torino, Italy Rolf Drechsler, University of Bremen, Germany Lydie du Bousquet, Laboratoire d'Informatique de Grenoble, France

Stephan Eggersglüß, German Research Center for Artificial Intelligence (DFKI) & University of Bremen, Germany Khaled El-Fakih, American University of Sharjah, UAE Robert Eschbach, Fraunhofer IESE - Kaiserslautern, Germany Leire Etxeberria, Mondragon University, Spain Florian Fankhauser, Vienna University of Technology, Austria Eitan Farchi, IBM Haifa Research Laboratory, Israel Michael Felderer, University of Innsbruck, Austria Teodor Ghetiu, University of York, UK Patrick Girard, LIRMM, France Debasis Giri, Haldia Institute of Technology - Purba Medinipur, India Hans-Gerhard Gross, Delft University of Technology, The Netherlands Jon Hall, Open University, UK Kazumi Hatayama, Nara Institute of Science and Technology, Japan Florentin Ipate, IFSoft, Romania David Kaeli, Northeastern University - Boston, USA Teemu Kanstrén, VTT Technical Research Centre of Finland, Finland Alexander Klaus, Fraunhofer IESE - Kaiserslautern, Germany Philippe Lahire, Université de Nice Sophia-Antipolis, France Abel Marrero, Daimler Center for Automotive IT Innovations - Berlin, Germany Julio Medina, Universidad de Cantabria, Spain Seda Ogrenci Memik, Northwestern University - Evanston, USA Atif Memon, University of Maryland, USA Mercedes G. Merayo, Universidad Complutense de Madrid, Spain Maria K. Michael, University of Cyprus - Nicosia, Cyprus Roy Oberhauser, Aalen University, Germany Juho Perälä, VTT Technical Research Centre of Finland, Finland Eric Piel, Technical University of Delft, The Netherlands Miodrag Potkonjak, Univeristy of California, Los Angeles (UCLA), USA Wishnu Prasetya, Utrecht University, The Netherlands Paolo Prinetto, Politecnico di Torino, Italy Andreas Raabe, fortiss --- An-Institut der Technischen Universität München, Germany Henrique Rebêlo, Federal University of Pernambuco, Brazil Michel Renovell, LIRMM, France Filippo Ricca, University of Genoa, Italy Thomas Rings, University of Göttingen, Germany Vladimir Rubanov, Institute for System Programming / Russian Academy of Sciences (ISPRAS), Russia Goiuria Sagardui, Mondragon University, Spain Christian Schanes, Vienna University of Technology, Austria Cristina Seceleanu, Mälardalen University, Sweden Amit Prakash Singh, Guru Gobind Singh Indraprastha University - Delhi, India Alin Stefanescu, University of Pitesti, Romania Dinesh Subhraveti, IBM Almaden Research Center - San Jose, USA Mehdi Tahoori, Karlsruhe Institute of Technology (KIT), Germany Michael Tautschnig, University of Oxford, UK Nur A. Touba, University of Texas - Austin, USA Spyros Tragoudas, Southern Illinois University Carbondale, USA

Dragos Truscan, Åbo Akademi University - Turku, Finland Eric Verhulst, Altreonic, Belgium Bart Vermeulen, NXP Semiconductors, The Netherlands Arnaud Virazel, Université de Montpellier 2 / LIRMM, France Tanja Vos, Universidad Politécnica de Valencia, Spain Stefan Wagner, Technische Universität München, Germany Melanie Ware, University of Ulster - Jordanstown, UK Sebastian Wieczorek, SAP AG - Darmstadt, Germany Cemal Yilmaz, Sabanci University - Istanbul, Turkey Zeljko Zilic, McGill University, Canada

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

## **Table of Contents**

| Using Assertion-Based Testing in String Search Algorithms<br>Ali Alakeel and Mahmoud Mhashi                                                                                | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

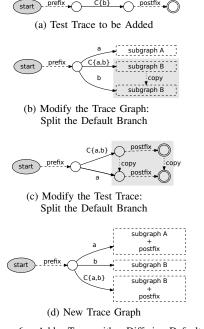

| An Approach to Modularization in Model-Based Testing<br>Teemu Kanstren, Olli-Pekka Puolitaival, and Juho Perala                                                            | 6  |

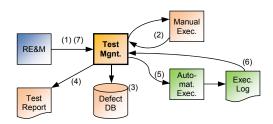

| Dealing with Challenges of Automating Test Execution<br>Vitalina Turlo and Valery Safronau                                                                                 | 14 |

| Detecting Equivalent Mutants by Means of Constraint Systems<br>Simona Nica, Mihai Nica, and Franz Wotawa                                                                   | 21 |

| Answer-Set Programming as a new Approach to Event-Sequence Testing<br>Esra Erdem, Katsumi Inoue, Johannes Oetsch, Jorg Puhrer, Hans Tompits, and Cemal Yilmaz              | 25 |

| A Test Case Suite Generation Framework of Scenario Testing<br>Ting Li, Zhenyu Liu, and Xu Jiang                                                                            | 35 |

| Is Mutation Testing Scalable for Real-World Software Projects?<br>Simona Nica, Rudolf Ramler, and Franz Wotawa                                                             | 40 |

| Testing As A Service for Component-based Developments<br>Hien Le                                                                                                           | 46 |

| A Zone-based Reachability Analysis of Variable Driven Timed Automata<br>Omer Nguena-Timo and Antoine Rollet                                                                | 51 |

| Retrospective Project Analysis Using the Expectation-Maximization Clustering Algorithm Steffen Herbold, Jens Grabowski, and Stephan Waack                                  | 58 |

| Extracting and Verifying Viewpoints Models in Multitask Applications<br>Selma Azaiez, Belgacem Benhedia, and Vincent David                                                 | 64 |

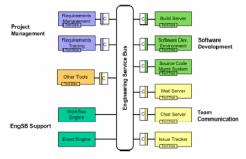

| Requirements and Solutions for Tool Integration in Software Test Automation<br>Bernhard Peischl, Rudolf Ramler, Thomas Ziebermayr, Stefan Mohacsi, and Christoph Preschern | 71 |

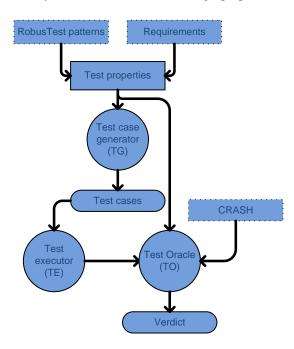

| RobusTest: Towards a Framework for Automated Testing of Robustness in Software<br>Ali Shahrokni and Robert Feldt                                                           | 78 |

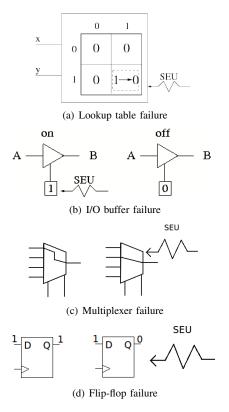

| Simulated Injection of Radiation-Induced Logic Faults in FPGAs                                                                                                             | 84 |

| Cinzia Bernardeschi, Luca Cassano, Andrea Domenici, Giancarlo Gennaro, and Mario Pasquariello                                                                                                                     |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Concurrent Engineering used to Implement Risk & Hazard Control<br>Gheorghe Florea and Luiza Ocheana                                                                                                               | 90  |

| Model Reconstruction: Mining Test Cases<br>Edith Werner and Jens Grabowski                                                                                                                                        | 97  |

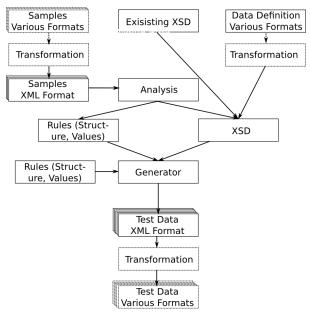

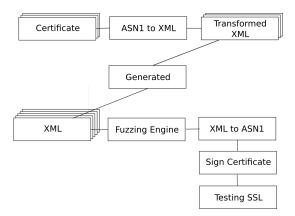

| Generic Data Format Approach for Generation of Security Test Data<br>Christian Schanes, Florian Fankhauser, Stefan Taber, and Thomas Grechenig                                                                    | 103 |

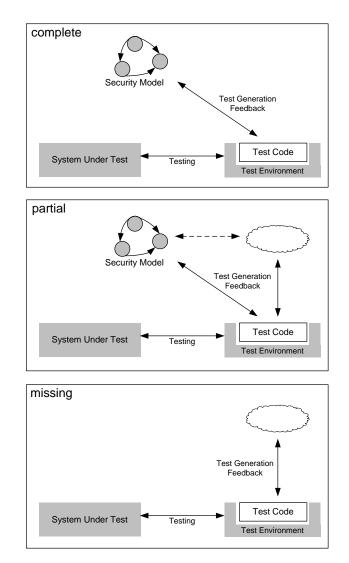

| A Classification for Model-Based Security Testing<br>Michael Felderer, Berthold Agreiter, Philipp Zech, and Ruth Breu                                                                                             | 109 |

| Utilizing Domain-Specific Modelling for Software Testing<br>Olli-Pekka Puolitaival, Teemu Kanstren, Veli-Matti Rytky, and Asmo Saarela                                                                            | 115 |

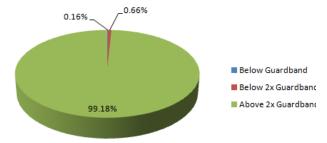

| Comparison of off-chip interconnect validation to field failures<br>Michael Shepherd, David Blankenbeckler, and Adam Norman                                                                                       | 121 |

| Software Testing in Critical Embedded Systems: a Systematic Review of Adherence to the DO-178B Standard Jacson Rodrigues Barbosa, Marcio Eduardo Delamaro, Jose Carlos Maldonado, and Auri Marcelo Rizzo Vincenzi | 126 |

1 1 4

Cinaia

1. 1

Andrea

$\cdot \cdot \alpha$

## Using Assertion-Based Testing in String Search Algorithms

Ali M. Alakeel<sup>1</sup> and Mahmoud M. Mhashi<sup>2</sup> College of Computers and Information Technology University of Tabuk P.O.Box 1458, Tabuk 71431, Saudi Arabia alakeel@ut.edu.sa<sup>1</sup> mmhashi@ut.edu.sa<sup>2</sup>

Abstract—Software programs may contain faults that cause them to work improperly. Assertion-Based testing has been shown to be effective in detecting program faults as compared to traditional black-box and white-box software testing methods. String search algorithm problem is one of the most important problems that had been investigated by many studies to find all the occurrences of a pattern (with size m characters) occurs in text (with size n characters), where m<<n. String search algorithms are one of the main elements of Information Retrieval Systems which are found in a wide range of applications such as military applications, aircraft software, medical applications, and commercial applications. Therefore, the correctness of any string search algorithms is vital. Different errors might occur during the implementation of any of these algorithms. An example of error, if the shift distance becomes zero, then the algorithm will not move forward. In this research, we show that Assertion-Based software testing may be effective in uncovering software faults associated with string searching algorithms. Our preliminary experimentation with this approach shows that several types of errors associated with string searching algorithms are uncovered using Assertion-Based software testing.

Keywords-Software testing; Assertion-Based Testing; Program Assertions; String Search Algorithms.

#### I. INTRODUCTION

Software programs may contain faults that cause them to work improperly. The effects of software failure could be very disastrous and life threatening. For example, a software failure may cause an airplane to crash, a nuclear factory to meltdown or even to cause a military missile to hit the wrong target, e.g., [22]. For this reason, software testing methods has gained so much attention from researchers and industry practitioners since computers were invented.

Software testing is a very labor intensive task and cannot by any means guarantees the correctness of any software or that the software is error-free. However, thorough and rigorous software testing may increase the confidence in the software under test. There are two main approaches to software testing: Black-box and White-box. Test data generation is the process of finding program input data that satisfies a given criteria. Test generators that support black-box testing create test cases by using a set of rules and procedures; the most popular methods include equivalence class partitioning, boundary value analysis, cause-effect graphing. White-box testing is supported by coverage analyzers that assess the coverage of test cases with respect to executed statements, branches, paths, etc. Programmers usually start by testing their software using black-box methods against a given specification. By their nature black-box testing methods might not lead to the execution of all parts of the code. Therefore, this method may not uncover all faults in the program. To increase the possibility of uncovering program faults, white-box testing is then used to ensure that an acceptable coverage has been reached, e.g., branch coverage.

Assertion-Based testing [4-5, 7] has been shown to be effective in detecting program faults as compared to traditional black-box and white-box software testing methods. Given an assertion *A*, the goal of Assertion-Based testing is to identify program input for which *A* will be violated. The main aim of Assertion-Based Testing is to increase the developer confidence in the software under test. Assertion-Based Testing is intended to be used as an extra and complimentary step *after* all traditional testing methods have been performed to the software. Assertion-Based Testing gives the tester the chance to think deeply about the software under test and to locate positions in the software that are very important with regard to the functionality of the software. After locating those important locations, assertions are added to guard against possible errors with regard to the functionality performed in these locations.

String search algorithms are one of the main elements of Information Retrieval Systems (IRS) which are found in a wide range of applications such as military applications, aircraft software, medical applications, and commercial applications. If an information retrieval system fails to return the correct piece of information, the results could be disastrous. For example, if a medical information retrieval system fails to return the *exact* prescribed medicine, this action may jeopardize the patient's life. Also, if a missile control system fails to retrieve the exact coordinates of the target, the results could be disastrous. Therefore, the correctness of any string search algorithms is vital. String searching algorithms are so fundamental that most computer programs use them in one form or another.

In this paper, we show that Assertion-Based software testing [4-5, 7] may be effective in uncovering software faults associated with string searching algorithms. Since the time Assertion-Based testing was proposed in [4] and to the best of our knowledge, this research is the first to present an application a proposed testing methodology, i.e., Assertion-Based testing, to a well known reported algorithms, i.e., string search algorithms. For the purpose of this research we have selected a number of well-known published string searching algorithms, gave them to programmers to implement them and then used Assertion-Based software testing to test these

implementations. Our result is presented in a case study presented in Section IV of this text. It should be noted that the efficiency, performance or the competency of each string search algorithm, considered in our study, are not questioned. Our main objective is to show that Assertion-Based testing may be effective during the development and testing of such algorithms.

The rest of this paper is organized as follows. Related work is discussed in Section II. Section III presents an application of Assertion-Based software testing method to the string search algorithms. In Section IV, we present a case study, followed by our conclusion and future work in Section V.

#### II. RELATED WORK

#### A. String Search Algorithms

Exact string searching is one of the most important problems that had been investigated by many studies, e.g., [8-21]. The problem of string searching may be stated as follows. Given a text string (Text) of size n and a pattern string (Pat) of size m (where  $n \gg m$ ), find all occurrences of *Pat* in *Text* [8].

As reported in the literature, many exact string searching and pattern matching algorithms were introduced and their performance was investigated against classical exact string searching algorithm such as Naïve (brute force) algorithm and Boyer-Moore-Horsepool (BMH) algorithm. Some of these algorithms preprocess both the text and the pattern, e.g., [9] while others need only to preprocess the pattern, e.g., [10, 11]. In all cases, the exact string searching problem consists of two major steps: checking and skipping. The checking step itself consists of two phases:

1) A search along the text for a reasonable candidate string

2) A detailed comparison of the candidate against the pattern to verify the potential match.

Some characters of the candidate string must be selected carefully in order to avoid the problem of repeated examination of each character of text when patterns are partially matched. Intuitively, the fewer the number of character comparisons in the checking step the better the algorithm is. Different string search algorithms may differ in the way they implement the checking process, e.g., [12, 13]. After the checking step, the skipping step shifts the pattern to the right to determine the next position in the text where the substring text can possibly match with the pattern. The reference character is a character in the text chosen as the basis for the shift according to the shift table. Some string search algorithms may use one or two reference characters and the references might be static or dynamic [14, 15]. Additionally, some algorithms focus on the performance of the checking operation while others focus on the performance of the skipping operation [16]. The shift distance used may differ from one string search algorithm to another; it ranges from only one position in the Naïve algorithm, up to m positions in Boyer-Moore-Horspool algorithm [11], m+1 positions in Raita's algorithm [10], and up to 3m+1 positions in CSA algorithm [17].

From the previous discussion, it can be noticed that there are different factors and elements of string search algorithms

that may lead to program errors during the implementations of these algorithms into real program's code. Some of these elements are the starting point of checking, the direction of checking, the skipping strategy, the number of static or dynamic reference characters, and different shift distances. Thus it is possible that errors might occur during the implementation of any string searching algorithm. For instance, the shift distance might become zero or the number of occurrences of *Pat* in *Text* found by the algorithm might be less than or greater than the actual occurrences of *Pat* in *Text*. In a case study, presented in Section IV, we found out that Assertion-Based testing may be effective in catching some of the faults associated with string search algorithms.

#### B. Assertion-Based Softwre Testing

Assertions are recognized as a supporting aid in revealing faults during software testing, debugging and maintenance, e.g., [1-7]. Therefore, many programmers place them within their code in positions considered error prone or have the potential to lead to software crash or failure. An Assertion specifies a constraint that applies to some state of computation. The state of an assertion is represented by two possible values: *true* or *false*. For example, *assert*(0<index<=100), is an assertion that constraints the values of some variable "index" to be in the range of 1 and 100 inclusive. As long as the values of "index" is within the allowed range the state of this assertion is *true*. Any other values beyond this range, however, will cause the state of this assertion.

Many programming languages support assertions by default, e.g., Java and Perl. For languages without built-in support, assertions can be added in the form of annotated statements. For example, [4] presents assertions as commented statements that are pre-processed and converted into Pascal code before compilation. Many types of assertions can easily be generated automatically such as boundary checks, division by zero, null pointers, variable overflow/underflow, etc. Beyond simple assertions that can easily be generated automatically, reference [4] presents a method to generate more complex assertions for Pascal programs. For this reason and to enhance their confidence in their software, programmers may be encouraged to write more programs with assertions.

It should be noted that writing the proper type of assertions and choosing the proper locations to inject them into programs depend heavily on the tester's experience and knowledge of the program under test. As mentioned previously, a simple tool may be used to automatically generate assertions in certain locations of the program which guard against errors such as division by zero, array boundary violations, uninitialized variables, stack overflow, null pointer assignment, pointer out of range, out of memory (heap overflow), and integer / float underflow and overflow [3]. However, there are applicationspecific locations in the program itself that may need to be guarded by assertions depending on the importance of these locations to the correctness of the application. For example, in string searching algorithms, computing the location of the pattern in the input string and index manipulation during the checking and skipping process are very important to the correctness of such algorithms.

1 #include <iostream> 2 #include <iomanip> 3 #include <cstring> 4 using std::cout; 5 using std::cin; 6 #define ASIZE 300 #define XSIZE 300 7 8 void preBmBc(char \*x, int m, int bmBc[]) { 9 int i. 10 for (i = 0; i < ASIZE; ++i)11 bmBc[i] = m; for (i = 0; i < m - 1; ++i){ 12 /\* A1: (x[i]>=0 and x[i]<ASIZE) \*/ // Assertion No. 1 13 bmBc[x[i]] = m - i - 1;14 void suffixes(char \*x, int m, int \*suff) { 15 int f, g, i; 16 suff[m - 1] = m;17 g = m - 1; 18 for (i = m - 2; i >= 0; --i) { /\* A2: (i + m - 1 - f)>=0 and (i + m - 1 - f)<XSIZE) \*/ // Assertion No. 2 19 if  $(i > g \&\& suff[i + m - 1 - f] < i - g){$ /\* A3: (i)>=0 and (i)<XSIZE) \*/ // Assertion No. 3 20 suff[i] = suff[i + m - 1 - f];21 else { 22 if (i < g)23 g = i; 24 **f** = i; 25 while  $(g \ge 0 \&\& x[g] == x[g + m - 1 - f])$ 26 --g; /\* A4: (i)>=0 and (i)<XSIZE) \*/ // Assertion No. 4 27 suff[i] = f - g;} } } 28 void preBmGs(char \*x, int m, int bmGs[]) { 29 int i, j, suff[XSIZE]; 30 suffixes(x, m, suff); 31 for (i = 0; i < m; ++i)32 bmGs[i] = m;33 j = 0; 34 for  $(i = m - 1; i \ge 0; --i)$ 35 if (suff[i] == i + 1)

Figure 1. Boyer-Moore Algorithm with Assertions

During our case study presented in Section IV, assertions were injected in locations that are error-prone and crucial to the correctness of a string search algorithm. This knowledge is gained through our investigation of each string search algorithm considered during our experiment.

#### III. USING ASSERTION-BASED TESTING IN STRING SEARCH ALGORITHMS

In this section, we present an application of Assertion-Based software testing to the Boyer–Moore string search algorithm [11]. Our complete case study is presented in section IV.

#### A. Boyer–Moore Algorithm

The Boyer–Moore string search algorithm [11] is a particularly efficient string searching algorithm. It has been the standard benchmark for the practical string search literature. The algorithm preprocesses the target string (key) that is being

36 for (; j < m - 1 - i; ++j) 37 if (bmGs[i] == m)38 bmGs[j] = m - 1 - i;39 for  $(i = 0; i \le m - 2; ++i)$ /\* A5: (m - 1 - suff[i])>=0 and (i)<XSIZE) \*/ // Assertion No. 5 bmGs[m - 1 - suff[i]] = m - 1 - i;40 void BM(char \*x, int m, char \*y, int n) { 41 int i, j, bmGs[XSIZE], bmBc[ASIZE]; 42 /\* Preprocessing \*/ preBmGs(x, m, bmGs); 43 44 preBmBc(x, m, bmBc); /\* Searching \*/ 45 j = 0;46 while  $(j \le n - m)$  { 47 for  $(i = m - 1; i \ge 0 \&\& x[i] == y[i + j]; --i);$ if (i < 0) { 48 49 cout<<"\nAn occurrence at location "<<j; 50 j += bmGs[0];51 else{ /\* A6: (i>=0 and i<XSIZE) \*/ // Assertion No. 6 /\* A7: ((y[i + j])>=0 and (y[i + j])<ASIZE) \*/ // Assertion No. 7 52 if(bmGs[i] > bmBc[y[i+j]] - m + 1 + i)53 j += bmGs[i];54 else 55 j += bmBc[y[i + j]] - m + 1 + i;} } 56 int main() 57 char Text[] = "test This is a test for string test"; 58 char Pat[] = "test"; 59 int m = 4; 60 int n = 35;61 cout << "\nInput text: " << Text << "\nPattern: " << Pat; 62 BM(Pat, m, Text, n); 63 cout << "\n Press ENTER to exit ...."; 64 getchar(); 65 return 0. }

searched for, but not the string being searched in (unlike some algorithms that preprocess the string to be searched and can then amortize the expense of the preprocessing by searching repeatedly). The execution time of the Boyer-Moore algorithm, while still linear in the size of the string being searched, can have a significantly lower constant factor than many other search algorithms: it doesn't need to check every character of the string to be searched, but rather skips over some of them. Generally the algorithm gets faster as the key being searched for becomes longer. Its efficiency derives from the fact that with each unsuccessful attempt to find a match between the search string and the text being searched, it uses the information gained from that attempt to rule out as many positions of the text as possible where the string cannot match. Figure 1 shows an implementation of Boyer-Moore Algorithm after assertions have been added to it. In this program we inserted a total of seven assertions in different positions of the code. Assertions are numbered and shown in **bold** in Figure 1.

After applying Assertion-Based Testing to Boyer-Moore Algorithm of Figure 1 Assertion #2 was *violated*. As described in [4], during Assertion-Based Testing, each assertion found in the program under test is converted into a corresponding code during a pre-processing stage. For example, Assertion#2 of Figure 1 will be converted into the following code:

| 18.1   | if (!((i + m - 1 - f)>=0))                            |

|--------|-------------------------------------------------------|

| 18.1.1 | <pre>cout &lt;&lt; "\nAssertion 2a Violation!";</pre> |

| 18.2   | if (!((i + m - 1 - f) <xsize))< td=""></xsize))<>     |

| 18.2.1 | <pre>cout &lt;&lt; "\nAssertion 2b Violation!";</pre> |

Considering the above segment of code, according to Assertion-Based Testing presented in [4], Assertion#2 is violated if either of statements 18.1.1 or 18.2.1 is executed. During our experiment, Assertion #2 was violated through the execution of statement 18.1.1. The violation of Assertion #2 has detected a fault in this program which is caused by the use of an uninitialized variable "f" used in statement#19 in Figure 1. Note that uninitialized variables might cause very serious bugs in the program due to the nondeterministic values those variables might take during the course of different program executions. It should also be noted that many forms of uninitialized variable go undetected by C++ compiler.

#### IV. CASE STUDY

For the purpose of this case study, we have selected, from the literature, seven different string searching algorithms. These algorithms are implemented in C++ by three programmers with more than 5 years of experience in software development. C++ language was selected because it is widely used in the industry in our area and in America. The programs are executed and tested using traditional software testing methods. Specifically the following software testing methods were used: black-box testing as represented by boundary value analysis and equivalence class partitioning while white-box testing is represented by branch coverage. Using these traditional software testing methods, we were not able to uncover any faults in any of the seven programs. As stated in [4], Assertion-Based testing is intended to be used as an extra and complimentary step after all traditional testing methods have been performed to the software. Assertion-Based Testing gives the tester the chance to think deeply about the software under test and to locate positions in the software that are very important with regard to the functionality of the software. After locating those important locations, assertions are added to guard against possible errors with regard to the functionality performed in these locations. Therefore, and in order to uncover any faults, we injected assertions in certain locations of each of the selected string search algorithms used in this study and then applied Assertion-Based Testing as described in [4]. As reported in Table I, we were able to uncover program faults, in all of the seven programs, which were left uncovered by traditional software testing methods or by tests performed by the original authors of those string matching algorithms.

Information presented in Table I may be interpreted as follows. Column#1 and Columun#2 show the name of the string search algorithm and the number of assertions inserted in each one, respectively. Column#3 shows the number of assertions that were violated during Assertion-Based software testing. For example, row#3 of Table I shows that in an implementation of the Horespool algorithm [18], a total of three assertions were inserted in this program. Two out the three assertions (66.7%) were violated during Assertion-Based testing. In this case study, the number of assertions ranges from 3 to 18 assertions. The percentage of assertion violations ranges from 5.5% to 66.7% and the percentage of the tested algorithms that contains faults was 100%. It should be noted that the result of this experiment might be different for different programs with different types of assertion-Based Testing [4-5, 7] may be effective in detecting program faults when applied to the considered set of string search algorithm implementations used in this experiment. We emphasize that the quality and the merits of the string search algorithms themselves are not questioned and is beyond the scope of this research.

| E I. CASAE STUDY RESULTS |

|--------------------------|

|--------------------------|

| Algorithm's Name      | #Assertions | #Violations |

|-----------------------|-------------|-------------|

| Boyer-Moore Algorithm | 7           | 1           |

| CSA Algorithm         | 13          | 1           |

| Horespool Algorithm   | 3           | 2           |

| KR Algorithm          | 4           | 1           |

| AXAMAC Algorithm      | 9           | 1           |

| COLUSSI Algorithm     | 18          | 1           |

#### V. CONCLUSION and FUTURE WORK

In this paper, we presented a new approach in which Assertion-Based testing is utilized to find software faults associated with string searching algorithms. We performed a case study in which a set of well-known string search algorithms are implemented and tested. During this case study, assertions were inserted in selected locations of each subject program to guard against possible errors. The result of this case study is encouraging and shows that Assertion-Based software testing was able to uncover faults in these programs that were overlooked by traditional software testing methods such as black-box and white- box testing. This result indicates that Assertion-Based testing may be very effective during the development and testing of string search algorithm. For our future research, we intend to extend our case study to include a wider range of string search algorithms especially those which function as a part of bigger commercial applications.

#### REFERENCES

- Stucki L. and Foshee G., "New Assertion Concepts for Self-Metric Software Validation," Proceedings of the International Conference on Reliable Software, pp. 59-71,1975

- [2] Yau S. and Cheung R., "Design of Self-Checking Software," Proceedings of the International Conference on Reliable Software, pp. 450-457, 1975.

- [3] Rosenblum, D., "Toward A Method of Programming WithAssertions," Proceedings of the International Conference on Software Engineering, pp. 92-104, 1992.

- [4] Korel B. and Al-Yami A., "Assertion-Oriented Automated Test Data Generation," Proc. 18th Intern. Conference on Software Eng., Berlin, Germany, pp. 71-80, 1996.

- [5] Alakeel A., "An Algorithm for Efficient Assertions-Based test Data Generation," Journal of Software, vol. 5, No. 6, pp. 644-653, 2010.

- [6] Korel B. and Alyami A., "Automated regression test generation," Proceedings of the 1998 ACM SIGSOFT international symposium on Software testing and analysis, pp. 143 – 152, 1998.

- [7] Alakeel A., "A Framework for Concurrent Assertion-Based Automated Test Data Generation," European Journal of Scientific Research, Vol. 46, No. 3, pp. 352-362, 2010.

- [8] Stephen G., "String Searching Algorithms", World Scientific, Singapore, 1994.

- [9] Fenwick P., "Fast string matching for multiple searches", Software–Practice and Experience, Vol. 31, No. 9, pp. 815–833, 2001.

- [10] Raita T., "Tuning the Boyer-Moore-Horspool String Searching Algorithm", Software Practice and Experience, Vol. 22, No. 10, pp. 879-844, 1992.

- [11] Boyer RS. and Moore JS., "A fast string searching algorithm", Communications of the ACM, Vol. 20, No. 10, pp. 762–772, 1977.

- [12] Ager M. S., Danvy O., and Rohde H. K., "Fast partial evaluation of pattern matching in strings", ACM/SIGPLAN Workshop Partial Evaluation and Semantic-Based Program Manipulation, San Diego, California, USA, pp. 3 – 9, 2003.

- [13] Fredriksson and Grabowski S., "Practical and Optimal String Matching", Proceedings of SPIRE'2005, Lecture Notes in Computer Science 3772, pp. 374-385, Springer Verlag, 2005.

- [14] Smith P., "On Tuning the Boyer-Moore-Horspool String Searching Algorithm", Short Communication, Software Practice and Experience, Vol. 24, No. 4, pp. 435-436, 1994.

- [15] Mhashi M., "The Effectof Multiple Reference Characters on Detecting Matches in String Searching Algorithms," Software Practice and Experience, Vol. 35, No. 13, pp. 1299 -1315, 2005.

- [16] Mhashi, M., "The Performance of the Character-Access On the Checking Phase in String Searching Algorithms", Transactions on Enformatica, Systems Sciences and Engineering, Vol. 9, pp. 38–43, 2005.

- [17] Mhashi M. and Alwakeel M, "New Enhanced Exact String Searching Algorithm" IJCSNS International Journal of Computer Science and Network Security, Vol. 10, No. 4, pp. 13 – 20, 2010.

- [18] Horspool R.N., "Practical fast searching in strings," Software -Practice & Experience, Vol. 10, No. 6, pp. 501-506, 1980.

- [19] Karp R.M. and Rabin M.O., 1987, "Efficient randomized pattern-matching algorithms, "IBM J. Res. Dev., Vol. 31, No. 2, pp. 249-260, 1987.

- [20] Apostolico A. and Crochemore M., "Optimal canonization of all substrings of a string," Information and Computation, Vol. 95, No. 1, pp. 76-95, 1991.

- [21] Colussi L., "Correctness and efficiency of the pattern matching algorithms," Information and Computation, Vol. 95, No. 2, pp. 225-251, 1991.

- [22] [http://www.pcworld.com/article/110035/software\_bug\_may\_ca use\_missile\_errors.html]. Last access date: July 26, 2011.

## An Approach to Modularization in Model-Based Testing

Teemu Kanstrén, Olli-Pekka Puolitaival, Juho Perälä VTT Technical Research Centre of Finland Oulu, Finland {teemu.kanstren, olli-pekka.puolitaival, juho.perala}@vtt.fi

*Abstract*—Test models in model-based testing are typically represented as state machines in terms of states and transitions. These states and transitions also are typically the focus of the test modeling approaches. Yet these test models are basically software components for the test automation domain, and need to be considered from test automation and software engineering viewpoints. In this paper, we describe a modeling approach that takes better into account these viewpoints. Taking these viewpoints into account, we propose a modularization approach for modeling in model-based testing and present a tool for supporting this modularization approach.

## Keywords-model based testing; test automation; modularization

#### I. INTRODUCTION

Model-based testing (MBT) is an advanced test automation technique focused on generating test cases from statebased models. In recent years several MBT tools have been presented and the industrial adoption of MBT techniques has been increasing [1,2]. The underlying modeling approach in these different tools is typically state-based, augmented by some programming language constructs to embed test instructions inside the test model to produce executable test cases from the state-machine transitions. The test generation is guided by the algorithms analyzing the model and parsing these programming language constructs to form test sequences and test data.

As such, this modeling approach can be seen as similar to other programming tasks. State transitions are executed to move from one state to another and these executions are performed in terms of programming language instructions embedded in these transitions. Yet the test modeling approach is based almost solely on state-machine notionstransitions between states and guard statements defining when transitions are allowed. While it is recognized that different domains and abstraction levels are important in MBT (e.g., [3]), the domain of test automation in itself is not considered in the common MBT modeling approaches. Relations between the test models and other software engineering artefacts are sometimes considered (e.g., [4]) but not the composition of the test models themselves. As these test models are in practice software components in themselves, we believe it is possible to provide a more efficient test modeling approach by introducing good practices from the software engineering domain, and specifically the software test automation domain into the test modeling approach itself.

Based on this background, we present a modularization approach for test modeling in MBT. This includes further modularization of the different traditional state-machine elements (transitions and guards) as well adding new ones specific to test automation (test oracles as specific transitions). We further present a modeling approach for describing test input and expected output in terms of a taxonomy of runtime invariance as described by our earlier work [5]. Finally, we identify a set of additional topics for future study that we believe will enable taking these approaches further. Similar to our inspiring domain of generic software engineering, we believe the end result helps achieve easier test model creation, evolution and maintenance. This forms a basis for more effective test modeling. The approach is implemented in a tool called OSMOTester, available as open-source [6].

The rest of the paper is structured as follows. Section II describes the background concepts relevant to this paper. Section III describes our test model modularization approach. Section IV discusses the concept in a wider context. Finally, conclusions summarize the paper and future works.

#### II. PRELIMINARIES

This section introduces the background concepts relevant for this paper.

#### A. Modularization

Modularization is one of the basic concepts in software engineering in general. Van der Hoek and Lopez [7] provide an overview of software modularization and its different aspects in software engineering. They show how modularization has been considered important from the early days of programming and has since evolved to all aspects of modern software engineering, and continues to be an important research question. The aspects they describe include programming languages, software architectures and software evolution. They also note the need to avoid excess modularization where not necessary. In terms of addressing modularity, van der Hoek and Lopez [7] list a number of benefits such as reduced complexity, enabling parallel work, enabling evolution (easier understanding, resilience to change, etc.), and easing reuse. The cost is described in terms of requiring added effort for composition of the modular pieces to form a whole

While this shows that modularity is considered important and is addressed in many software engineering domains, the consideration in MBT has focused on state-machine concepts [8] and not considered modularization in terms of test automation concepts and model elements generally. These are the concepts we address in this paper, in providing extended means to express modularity in test models, including important test automation concepts, and in mitigating the costs by providing automated support for module composition.

Considering modularity in software engineering in general, Sarkar et al. [9] list seven main properties of modularity. *Similarity of purpose* refers to grouping together elements related to providing a specific service. *Encapsulation* refers to encapsulating the internals of a module from its environment and external collaborators. *Compilability* refers to possible issues in compiling a module due to issues such as circular dependencies. *Extensibility* refers to providing means to extend a specific module without accessing its internals. *Testability* refers to the ease of testing the module. *Cyclic dependencies* negate many of the benefits of modularization and as such need to be avoided. *Module size* should be overall roughly equal. In the following sections we present our approach in Section IV also discuss how it relates to these properties.

#### B. Example System

Throughout the rest of this paper, we will use a simple vending machine example to illustrate the concepts discussed. This vending machine is a modified version of the example used in [2]. The relevant part of the operation of the machine can be described as the set of following properties:

- Accepts 10, 20, and 50 cent coins.

- When a total of 100 cents have been inserted the action *vend* is enabled.

- When *vend* is enabled, no more coins can be inserted (this assumption is relaxed later).

- When *vend* is activated, a bottle is produced, reducing the total number available and resetting the number of inserted cents to 0.

- When the machine is empty (no bottles), all actions are disabled.

Notice that for the sake of providing a concise example, this model simplifies several aspects such as providing change to the user when going over the total of 100 cents.

#### C. Model-Based Testing

The term model-based testing (MBT) can be defined in different ways. We follow Utting and Legeard [2] who describe MBT as "Generation of test cases with oracles from a behavioural model". The model describes the expected behaviour of the system under test (SUT), and is used by a MBT tool in order to generate test cases, in a form suitable for the test target, such as method invocation sequences and input data. The SUT output is checked by the test oracles also encoded into the model.

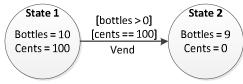

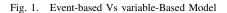

A typical model applied in the context of MBT is based on some form of states and transitions (sometimes referred to as pre/post conditions, historical or functional notations [8]), such as an extended finite state machine (EFSM). This describes the system behaviour in terms of states and transitions between these states. Basically a state can be described as a relevant combination of system internal variables. A transition forms an invocation of some functionality of the SUT, possibly affecting the observed state. Finally, guard statements over the transitions impose constraints on when a transition is allowed to happen. To illustrate these concepts, Figure 1 shows an example snippet of a state-machine for the vending machine. In this example, *state 1* is where the machine includes 10 bottles and 100 cents have been inserted. As defined by the example guard statements, the *vend* transition to *state 2* is allowed if there are bottles available in the machine and 100 cents have been inserted.

Figure 1. Vending machine model snippet.

In this case, both of these conditions have been met and thus this transition is enabled. Once it is taken, the number of bottles is reduced to 9 as one is deducted and the number of inserted cents is reset to zero. In this example, state is composed of the number of bottles available as well as the number of inserted cents.

To produce suitable test cases from such a model, this information is then transformed to test data for the SUT as defining the input to be given to invoke this transition on the SUT. This can be, for example, a message to the vending machine to produce a *vend* action. This is information encoded into the model by the user.

The test model must also define the expected output for each taken transition (the test oracle) in order to validate the correctness of the responses from the SUT for the given input. For example, the *vend* request should impact the reported number of bottles and produce a response as the "bottle" itself. This can be encoded in the test model along with the transition as an expected result, forming a test oracle.

Thus, to produce a suitable test model, the model must embed in itself means to identify test input to stimulate the SUT, the expected output for each input to produce a test oracle that gives verdict if the test passes or not, and a test harness that actually links the execution of the tests with the actual SUT.

#### III. TEST MODEL MODULARIZATION

The typical EFSM modeling notation for MBT was presented in the previous section. From this, we can list the following components that are needed to produce a suitable test model for test generation.

- Transitions to define what are the possible test steps for a specific SUT in its current state.

- A representation of the SUT state for the model.

- Test oracles to check the correctness of the received output and the internal state of the SUT when different transitions are taken.

- Guard statements to define when a specific transition is allowed to be taken.

- Test input to be linked to each transition/test step.

#### A. Traditional Modeling Approach for MBT

Figure 2 shows an example snippet of a test model for the vending machine, using the notation of the OSMOTester

MBT tool. This is based on existing works such as Model-JUnit described in [2], modified to better address the modularization aspects discussed in this paper. In this example, the variable *sut* represents the system and can either directly delegate the commands to the SUT itself or to a scripter writing a test script for later execution. The internal state of the model is composed of the *cents* and *bottles* variables. The guards are methods identified by the @*Guard* annotation and providing a Boolean value (*true* for allowing the transition). A transition is matched to its guard by the name given for both the (*@Transition* and *@Guard* annotations.

```

private int cents = 0;

private int bottles = 10;

private VendingMachine sut = new VendingMachine();

@Guard("10cents")

public boolean allow10cents() {

return cents <= 90 && bottles > 0;

@Transition("10cents")

public void insert10cents() {

sut.insert(10);

cents += 10;

assertEquals(cents, sut.cents());

@Guard("vend")

public boolean allowVend() {

return cents == 100;

@Transition("vend")

public void vend() {

sut.vend();

cents = 0;

bottles--;

assertEquals(cents, sut.cents());

assertEquals(bottles, sut.bottles());

```

Figure 2. Example model snippet.

Test oracles are represented inside the transitions by the *assertEquals()* method calls (here from the JUnit test framework [10]) that compare the state of the test model to the state of the SUT. Input is given to the SUT in each transition. For example, *sut.insert(10)* in the "10cents" transitions, where 10 represents the number of cents inserted.

This is an example of the traditional approach to MBT, where every transition encodes all test components, including test input, and test oracles. In this approach, there is also a direct mapping from a single guard to a single transition. This is how traditionally most MBT tools expect the test models to be provided and how they process them (see e.g., [1] for comparison).

Figure 2 also illustrated two basic aspects of a test model in the terminology of this paper. What we term as controlflow in this aspect is the way the MBT tool traverses the EFSM expressed by this model, in evaluating the guards and taking suitable transitions as chosen by the active test generation algorithm. Together with this, we use the term dataflow to describe how the state variable values of the model evolve as the MBT tool traverses over the control-flow. For the vending machine, this translates to the evolution of the *cents* and *bottles* variables over time.

#### B. Modularizing the Control-Flow Modeling

Besides representing the guards, transitions and states of the EFSM as their own components, the traditional approach presented in the previous subsection is not very modular. It does not consider the separation of the different aspects of test inputs and test oracles (and associated test output). Furthermore, by assuming a direct one-to-one mapping from guards to transitions, the flexibility of the EFSM modeling is limited. As these test models are in practice software components themselves, this leads to several problems from their evolution and maintenance viewpoints such as duplication, low cohesion and weak separation of concerns.

To address these issues, we introduce new test model components and refine existing components. This includes more advanced guard composition, extensions for more explicit test oracles as components of the test model itself, and objects for generating input data and evaluating output data. In this subsection we discuss the control-flow elements and in the following subsection the data-flow elements.

The typical approach to modeling guard statements in an EFSM is to provide a specific guard attached to a specific transition as illustrated by Figure 2, where both the *10 cents* and *vend* are transitions and have a single dedicated matching guard statement. Taking the guard statement for *10 cents* as an example, it provides assertions over two separate concepts, the number of bottles and the number of cents. To help separate these concerns and provide a manageable modeling notation, we extend guard modeling by allowing decomposition of guard statements for a transition into several separate guards, and to share a single guard statement across several transitions as needed.

The decomposition aspect is illustrated in Figure 3. This decomposition provides for more cohesive structure where different concerns are addressed by different guards. In this case, the checks over the different state variables have been split into separate guard statements, each mapping to their specific transition by their name (e.g., "10cents"). The end result is more cohesive guard and better separation of model concerns.

```

@Guard("10cents")

public boolean checkMaxCents() {

return cents <= 90;

}

@Guard("10cents")

public boolean checkBottles() {

return bottles > 0;

}

```

Figure 3. Guard decomposition.

However, decomposition alone does not fully address the need for providing cohesive guard statements over all the different transitions in the model. For example, if we consider the vending machine example, there are several transitions for inserting different types of coins (10, 20, 50 cents). In practice, none of these or the vend transition, should be allowed to execute if there are no bottles available. To support this, we need to provide specific shared guard statements.

This is illustrated in Figure 4 where the first guard *checkBottlesExist()* is shared by all transitions in the model,

and the second one is shared by the three listed transitions (10, 20, 50 cents). The first of these examples is an example suitable for our simple vending machine example as is. The second one is an example of how we might model a common guard in a case where the user is allowed to insert enough coins for several bottles at once and we need to check that the total of inserted coins does not go over the number of available bottles.

```

@Guard

public boolean checkBottlesExist() {

return bottles > 0;

}

@Guard({"10cents", "20cents", "50cents"})

public boolean allowMoreCoins() {

return bottles >= (cents/100);

}

```

Figure 4. Shared guard example.

In addition to having guards and transitions govern how test sequences are generated, we have to consider the evaluation of the test results. This is done by a test oracle and is traditionally part of each transition as shown in Figure 2 (the assert statements). In many cases, specific checks are needed for transitions to check their specific results. However, it is also commonly important to evaluate the general state of the model against the matching state in the SUT. To support more explicit modeling of test oracles, we extend our modeling notation to add general test oracles for program state over several transitions. These are similar in decomposition to the shared guards and identified by the @Oracle annotation. Figure 5 illustrates this with an example for the two state variables shown in Figure 2 for the vending machine. In practice, our MBT tool sees these as specific transitions to be executed between other transitions. It is also possible to relate them to specific transitions with the style of @Oracle("transition-name") similar to guards. In our models, generic oracles apply regardless of existence of specific ones. Any oracle matching a transition is always evaluated.

```

@Oracle

public void evaluateBottles() {

assertEquals(bottles, sut.bottles());

}

@Oracle

public void evaluateCents() {

assertEquals(cents, sut.cents());

}

```

Figure 5. Generic oracle example.

As these generic checks can be expressed separately and evaluated specifically by OSMOTester, they not only allow for the modular expression of generic test oracles but also add more power to the verification functionality of the test model and the MBT approach itself. In Figure 5, the state of the model and the state of the SUT are now evaluated to match continuously without the need to express them explicitly over each transition. Any deviation is thus captured as soon as it occurs and not possibly several transitions later in the *vend* transition (if at all) as was the case in Figure 2.

Finally, we also need to consider how and where test generation should be stopped. The typical approach in MBT

is to describe the test model as a state machine with the expectation that test cases can be generated and the model can be traversed at different points, where test generation should practically always be enabled. The choice of what transitions to take and when to stop the test generation is mainly up to the test generation algorithm. However, there are points where it is possible that no transition is enabled and the typical modeling approach gives no indication to test generation as to how this should be evaluated. The generic algorithms used to generate tests from the test model cannot know how to evaluate this condition for a specific SUT and its test model. For example, in the case of the vending machine example, if the *vend()* transition is taken 10 times, the number of bottles will reach zero and the shared guard checkBot*tlesExist()* will cause a state where no new transitions are available. At this point, the test generation tool cannot know if this should be treated as a failure or as a clue to end test generation for this step.

To enable the model to express this kind of information, we add a new annotation called *@EndCondition* and as illustrated in Figure 6. When a method with this annotation returns *true*, it is taken as an indicator that the current test generation from this model should be stopped and a new test case should be started. If no transitions are available and there is no *@EndCondition* that returns *true*, the current test case is reported by the tool as a failure. This will most likely indicate a problem in the test model itself. It should be noted that this annotation is not required for the test generation algorithms to stop test generation but they can also stop in other phases where found appropriate by the algorithm. It can also be used at any point to describe conditions to stop test generation, regardless of the state of the model.

We also provide specific notations for setting up new test cases and shutting down a running system using notations such as *@BeforeTest*, *@AfterTest*, *@BeforeSuite*, and *@AfterSuite*. We borrow these concepts from familiar tools such as JUnit [10] and TestNG [11], helping also to provide familiar concepts for other tool users. They basically define methods that are to be executed before and after a test case or a test suite respectively, regardless of the algorithms and end conditions.

```

@EndCondition

public boolean endIfNoBottles() {

return bottles == 0;

}

```

#### Figure 6. Expressing end conditions.

Using our new control-flow modeling notations we can thus produce the model shown in Figure 7. Notice that there is now only a single test oracle where all test assertions are centralized. The transitions can now focus on performing actions on the SUT and updating the model state accordingly. Also, the transition *10cents* no longer requires a guard statement as it is fully covered by the shared guard statement (also applying to *vend*). Finally, the model can no longer enter an unknown state as the end condition for a state with no bottles is explicitly specified.

```

private int cents = 0;

private int bottles = 10;

private VendingMachine sut = new VendingMachine();

@Guard

public boolean checkBottlesExist() {

return bottles > 0;

}

@Transition("10cents")

public void insert10cents() {

sut.insert(10);

cents += 10;

}

@Guard("vend")

public boolean allowVend() {

return cents == 100;

@Transition("vend")

public void vend() {

sut.vend();

cents = 0;

bottles--;

}

@Oracle

public void evaluateState() {

assertEquals(bottles, sut.bottles());

assertEquals(cents, sut.cents());

assertTrue(cents >= 0);

assertTrue (cents <= 100);

assertTrue(bottles >= 0);

@EndCondition

public boolean endIfNoBottles() {

return bottles == 0;

```

Figure 7. The model snippet in updated notation.

#### C. Modularizing the Data-Flow Modeling

The modeling notation described so far in the previous section shows how we can modularize the control-flow aspects of test modeling in MBT. From the viewpoint of dataflow we need to consider also the input- and output-data values and their respective constraints. Input data needs to be generated for the different parameters given to the SUT, and needs to respect the set of expected constraints for the SUT functions they are linked to. But since full coverage of most input combinations is not possible to achieve, we must also define a set of constraints to define what type of test data should be generated. The output must similarly consider the constraints for the output values received from the SUT as response to the provided stimuli (input).

To support modeling these data-flow constraints, we provide a generic library of objects we term as invariants objects. These are based on our previous work in identifying different aspects of runtime invariance in software behavior [5]. Each invariant object allows one to specify a set of constraints over the data value it represents and to use these as a basis to perform actions such as generate input data or evaluate the conformance of given (output) values. These allow for addressing data-flow invariance for a specific value in a single object, effectively modularizing the constraints over a single variable in a single object. An updated model for the vending machine using this notation is shown in Figure 8. This time, the use of the invariant objects for data-flow representation allows for a compact representation, and this includes transitions for all possible coin types and vending. By adding the shared guard and end condition from Figure 7 the model will include all the important model elements for the vending machine. The invariant objects presented in the figure are specified for integer data types, and we currently support the basic data types of integers, floating points, Booleans and character strings. The constraints supported by these are defined according to the taxonomy presented in [5].

Note that this model slightly changes the expected behavior of the vending machine towards a more realistic one. This specification now accepts any number of coins and deducts 100 from the number of inserted coins when *vend* is applied. It also collapses all *insertXXCents()* transitions (10, 20, 50) from the previous models into a single one, where the input is represented by a single invariant object defining the allowed input values. This is the *ci* object (short for *centInput* for space reasons in the figure) for the input value definitions. Test oracle expectations for both *cents* and *bottles* variables are expressed by the *co* and *bo* variables (short for *centOracle* and *bottleOracle* for space reasons in the figure).

```

private IntInvariant ci = new IntInvariant();

private IntInvariant co = new IntInvariant();

private IntInvariant bo = new IntInvariant();

public void TestModel() {

//set up allowed input values

ci.addValue(10);

ci.addValue(20);

ci.addValue(50);

//set up evaluation constraints

co.setMin(0);

bo.setMin(0);

bo.setMax(10);

}

@Transition("insertCoins")

public void insertCents() {

int coin = ci.input();

sut.insert(coin);

cents += coin;

@Guard("vend")

public boolean allowVend() {

return cents >= 100;

@Transition("vend")

public void vend() {

sut.vend();

cents -= 100;

bottles--;

@Oracle

public void evaluateState() {

assertEquals(bottles, sut.bottles());

assertEquals(cents, sut.cents());

co.evaluate(cents);

bo.evaluate(bottles);

```

Figure 8. Data-flow modularization.

#### D. Further modularization support

In the previous sections we have shown how to build a modularized test model in our notation. So far we have included the elements needed to build a useful model for generating test sequence and test data. Additionally, it is also important in test automation to be able to express how the generated test cases cover different requirements, a concept also supported by different MBT tools [2]. We support this through a special requirements object as illustrated in Figure 9. Note that defining the requirements twice is not required (add() and covered() methods) but doing so allows the tool to report the coverage percentage.

```

@RequirementsField

private Requirements req = new Requirements();

@TestSuiteField

private TestSuite s = null;

public TestModel() {

req.add("vend");

}

@BeforeTest

public void startTest() {

System.out.println("Starting Test "+s.count());

}

@Transition("vend")

public void vend() {

req.covered("vend");

...

}

```

Figure 9. Additional supported test model components.

Figure 9 also illustrates how the modeler can access the test generation history by adding a *TestSuite* field that will be initialized by the MBT tool before starting test generation. This provides useful information for evaluating and debugging the test model itself. It also allows the user access to the current test case object, for example, enabling the user to set the test case as passed or failed for any special reporting extensions in the MBT tool.

So far we have discussed several new notations for MBT that help produce more modular test models. However, an important question of decomposing the objects representing this notation remains. Besides expressing all elements in a single model, we also support decomposing the model objects into several sub-models. When these are registered into OSMOTester, it will parse them all and match all the expressed model elements into a single internal representation. This effectively allows one to, for example, represent the test oracles in one partial model, guards in another, transitions in a third, and the remaining ones in fourth. Merging is based on handling the model element naming across the different model objects as if they were one.

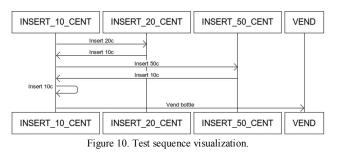

Finally, we also support the basic set of modular aspects for any MBT tool as discussed in [12]. It is possible to plug in different test generation algorithms, algorithms for defining length of generated test suites and test cases, and to attach various test harnesses and test analysis tools. Figure 10 shows an example of a test sequence visualization tool we provide as a plugin to the core OSMOTester itself, using as output a test listener interface provided by the core.

This visualization shows each transition in the test model as a box, and the sequences of transitions taken as arrows from one to another. In this case, the user has chosen to use "10cents" as the default state, which is why the arrows seem to originate from this box. This is just one of the available visualizations as an example of something that can be plugged in to describe the test cases.

#### E. Modularization Summary

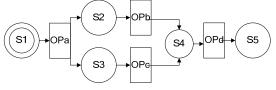

Figure 11 illustrates the overall flow of the different control-flow modules in our model. Before test suite generation commences, *@BeforeSuite* annotated methods are executed. Before each new test generation, *@BeforeTest* annotated methods are executed. *@Guard* methods are checked for enabled transitions, of which one is picked by the test generation algorithm. After each transition any associated *@Oracle* methods are executed. If *@EndConditions* exist, they are evaluated for stopping criteria for a single test case. If not, the criterion is left to the test generation algorithm. *@AfterTest* methods are executed when a test generation stops, and *@AfterSuite* when all test generation stops.

Data-flow support is defined in terms of invariant objects defining constraints over data-flow values that support generating input and evaluating output. Coverage requirements can be expressed in the test model as objects of their own, and models can be built from separate model objects as best seen fit. We see further developments in terms of more complex combinations of data-flow and control-flow elements as discussed next.

In relation to the different properties of modularization that were discussed in section II.A, we improve on several of these properties. Similarity of purpose is supported by more explicit grouping of elements such as test oracles. Extensibility is supported by allowing composition of the model elements (test steps/transition components) from several different objects and linking them automatically together. It is possible to add new test oracles, guards and other elements as separate model objects without touching existing ones (also helping address similarity composition). We avoid cyclic dependencies and enhance compilability by keeping elements separate and associating by the transition name metadata only (vs. strict static linking). Our framework is encapsulated in a set of simple annotations, providing only minimal exposure on the test models. We make *module size* easier to manage with finer granularity of model elements. Testability is mostly handled in itself by generating tests from the model and executing them against the SUT as in MBT in general, verifying both the test model and the SUT.

Figure 11. Control-Flow Summary.

#### IV. DISCUSSION

Modularization is one of the key aspects of good software engineering in general. As we have discussed and illustrated in the previous sections, test modeling in MBT is practically a software engineering activity in itself. It is basically about engineering a piece of software that generates a test suite in terms of the MBT framework, provided by available tools and libraries. While the traditional test modeling approaches for MBT have been lacking proper modularization mechanisms, we provide a set of means to achieve increased modularity in test modeling. This provides for increased separation of concerns, more cohesion and less duplication. As generally in software engineering, this helps achieve higher maintainability and supports model evolution.

While we advocate the use of our new modularized modeling notation, our approach also fully supports the more traditional modeling approach. It is possible to fully compose the model of transitions, guards and embedding all the information inside these without any modularization. This means just using a specific subset of our modeling notation (*@Transition* and *@Guard*). It is our experience that the best result in practice is to combine parts of the different approaches where most benefit can be gained. That is, modularizing the most common parts while keeping specific parts where it makes more sense according to the case at hand.

As our models are written in a standard programming language (Java), it is also possible to decompose the models into modules in terms of classes and methods. This can help achieve some of the benefits discussed here in itself (by using classes and objects), but it is also our experience that as the model is made more explicit in terms of generic test oracles, guards and invariant objects, this helps build a more explicit and understandable model. This also further helps in the model creation, evolution and maintenance, where human understanding is typically the key factor in software engineering. The use of a common programming language also helps more generic modularization as we can make use of the wide set of existing Java libraries.

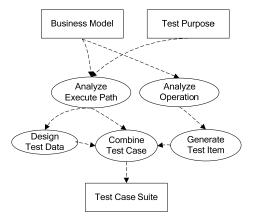

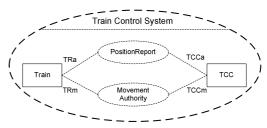

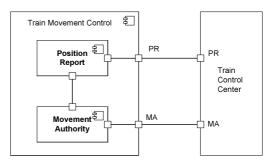

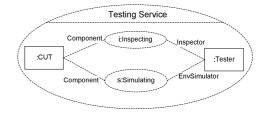

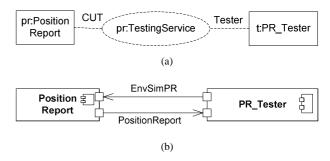

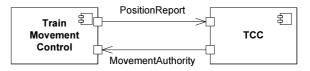

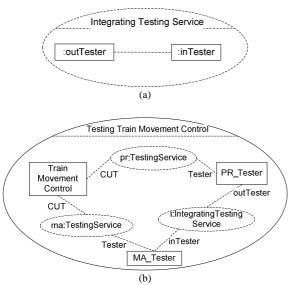

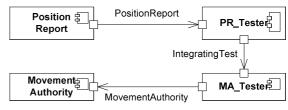

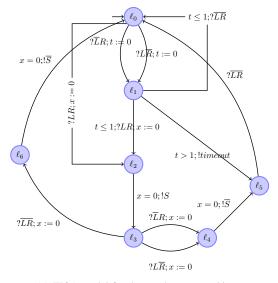

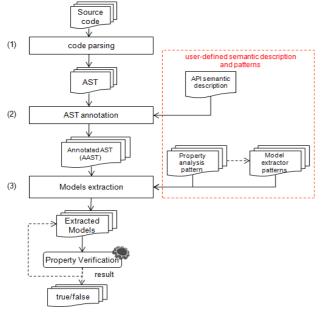

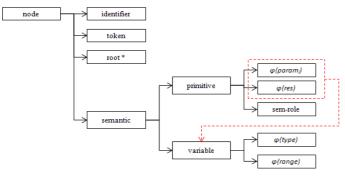

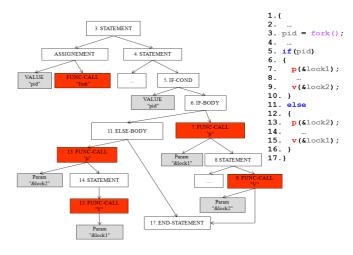

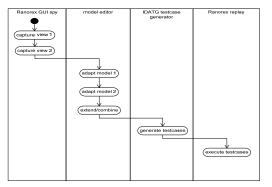

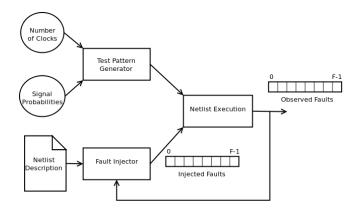

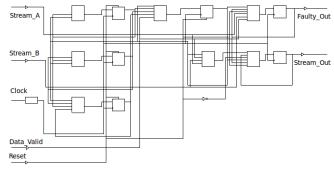

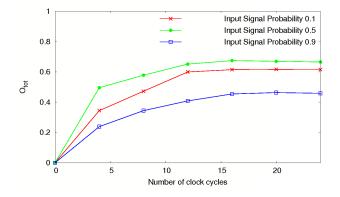

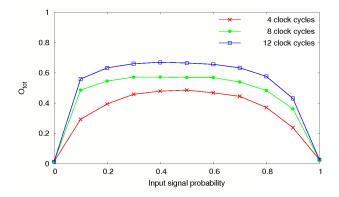

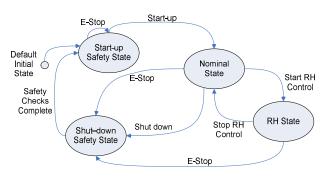

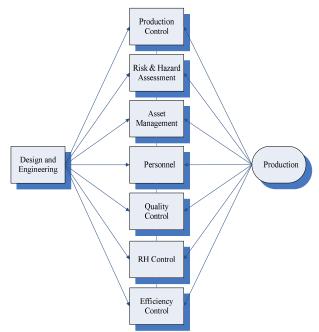

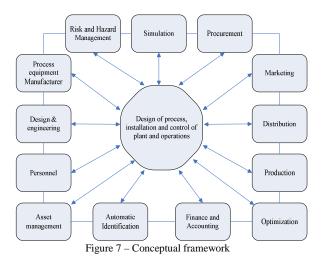

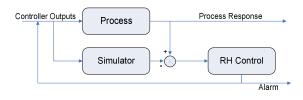

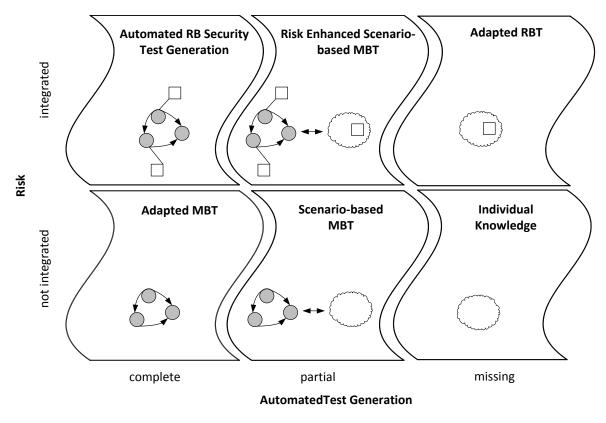

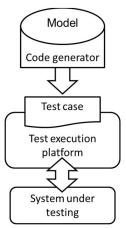

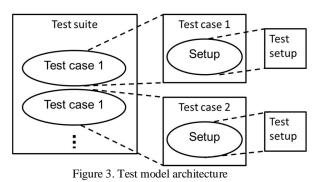

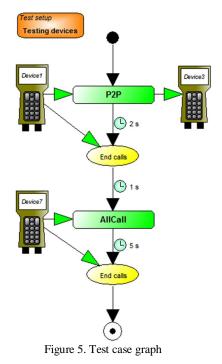

Another aspect related to the modularization of test models is the modularization of the test models into representing different viewpoints of the SUT behavior. While the test models we have presented in this paper describe the expected correct behavior of the vending machine, another interesting aspect is the modeling of the failure behavior of the SUT. In case of the vending machine, this would include trying to insert incorrect values, access the vending functionality with less than 100 coins, using negative values, and so on. These different viewpoints can be modeled as separate models addressing these specific constraints along with matching test oracle definitions. This is a form of modularization itself.